本文的主要內(nèi)容是現(xiàn)在MATLAB中產(chǎn)生仿真所需要的輸入信號,,以十六進制形式存放在數(shù)據(jù)文件中,,在modelsim中用verilog語言編寫測試文件,,做時序仿真,,后將結(jié)果存入另外一個數(shù)據(jù)文件,,后在matlab中將modelsim的仿真輸出文件讀入一個數(shù)組中,以便可以作圖分心,進一步做誤差分析。

雖然Modelsim的功能非常強大,,仿真的波形可以以多種形式進行顯示,但是當(dāng)涉及到數(shù)字信號處理的算法的仿真驗證的時候,,則顯得有點不足,。而進行數(shù)字信號處理是Matlab的強項,不但有大量的關(guān)于數(shù)字信號處理的函數(shù),,而且圖形顯示功能也很強大,,所以在做數(shù)字信號處理算法的FPGA驗證的時候借助Matlab會大大加快算法驗證的速度。

關(guān)于Matlab和Modelsim聯(lián)合仿真,,我從網(wǎng)上看到兩種方法,一種是通過Link for Modelsim建立Matlab和Modelsim的聯(lián)合仿真接口,;另一種就是通過文件讀寫的方式實現(xiàn)Matlab和Modelsim的聯(lián)合仿真 ,。關(guān)于第二種方法,只是通過幾個文件讀寫函數(shù)就可以實現(xiàn)了,,而且基本可以滿足當(dāng)前仿真的要求 ,。

1. Matlab產(chǎn)生數(shù)據(jù)用作Modelsim仿真

在FPGA進行算法驗證的時候,經(jīng)常需要輸入仿真數(shù)據(jù),,這些數(shù)據(jù)可以用FPGA產(chǎn)生,,但是如果數(shù)據(jù)產(chǎn)生過程很復(fù)雜的話,需要耗費很大的精力,,并且產(chǎn)生的數(shù)據(jù)的準(zhǔn)確性也不能保證,。例如,如果要驗證一個通信接收機的相關(guān)算法,,那么我們就需要先產(chǎn)生發(fā)送數(shù)據(jù),,也就是說得先做一個發(fā)射機,如果這個過程也由FPGA實現(xiàn)的話,,也是一個很復(fù)雜的過程,。這時候我們就可以借助Matlab,利用Matlab內(nèi)部自帶的各種函數(shù),,產(chǎn)生需要的信號,,再經(jīng)過定點化,就作為FPGA接收模塊的輸入信號了,。這樣做無疑會節(jié)約很多時間和精力,。

下面用一個簡單的例子說明如何用Matlab產(chǎn)生的數(shù)據(jù)用作Modelsim仿真。

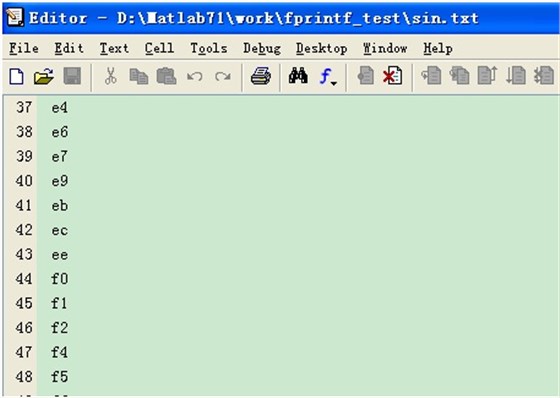

首先利用matlab產(chǎn)生一個周期256點8bit的正弦波數(shù)據(jù),,然后以16進制形式寫入sin.txt文件

N = 256;

n = 1:256;

x = fix(128 + (2^7 - 1) * sin(2*pi*n/N));

fid = fopen('sin.txt','wt');

fprintf(fid,'%x\n',x);

fclose(fid);

下圖是截取的產(chǎn)生的數(shù)據(jù)文件的內(nèi)容

然后將產(chǎn)生的sin.txt文件復(fù)制到Modelsim的工程下,,在Verilog文件中先定義一個8bit X 256數(shù)組,,然后通過$readmemh命令,將文件中的數(shù)據(jù)讀入,,相關(guān)的Verilog代碼如下:

reg [7:0] data_mem[0:255]; //定義一個8bit X 256的數(shù)組

initial

begin

$readmemh("sin.txt",data_mem); //將sin.txt中的數(shù)據(jù)讀入存儲器data_mem

end

關(guān)于$readmemh的用法可以參見Verilog的參考書,,這里就不詳細(xì)說了。

后面就可以用data_mem作為你的測試數(shù)據(jù)了,。例如可以通過以下代碼,,將data_mem的數(shù)據(jù)送給data_out:

always @(posedge clk)

begin

if(rst)

begin

data_out <= 8'd0;

i <= 8'd0;

end

else

begin

data_out <= data_mem[i]; //將存儲器中的數(shù)據(jù)輸出

i <= i + 8'd1;

end

end

這樣利用data_out就可以輸出一個正弦波波形,下圖是Molesim仿真產(chǎn)生的正弦波波形:

2. Matlab對Modelsim仿真生成的數(shù)據(jù)進行分析

Matlab對Modelsim仿真生成數(shù)據(jù)的處理也是通過文件讀寫實現(xiàn)的,。即通過Verilog語句,,將仿真過程中的某個信號寫入文件,然后在Matlab中在把這個文件的數(shù)據(jù)讀出來,,就可以在Matlab中進行分析了,。

下圖也通過一個簡單的例子,說明一下整個過程,。

以下的Verilog語句實現(xiàn)將信號data_out的數(shù)據(jù)寫入data_out.txt文件

integer w_file;

initial w_file = $fopen("data_out.txt");

always @(i)

begin

$fdisplay(w_file,"%h",data_out);

if(i == 8'd255) //共寫入256個數(shù)據(jù)

$stop;

end

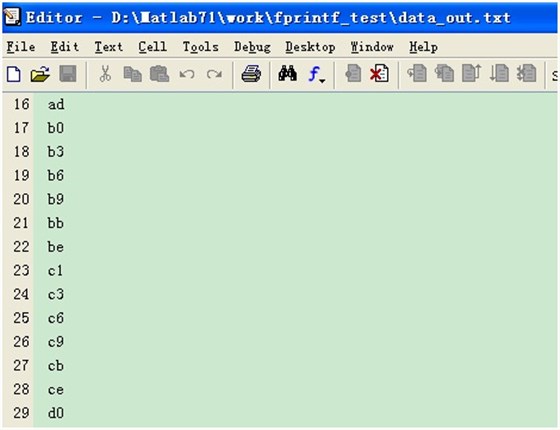

下圖是截取的data_out.txt的部分內(nèi)容:

然后就可以編一小段Matlab的程序?qū)ata_out.txt中的數(shù)據(jù)讀取進行分析了,。下面一段Matlab的程序是將數(shù)據(jù)讀取,并通過圖形顯示出數(shù)據(jù)的波形,。

fid = fopen('data_out.txt','r');

for i = 1 : 256;

num(i) = fscanf(fid, '%x', 1); %這句話的意思是從fid所指的文件以16進制方式讀出一個數(shù)據(jù),。

end

fclose(fid);

plot(num);

當(dāng)利用fscanf函數(shù)時要注意兩點,

:保證讀取的數(shù)據(jù)格式和文件中保存的數(shù)據(jù)格式是相同的,,例如這里文件中保存的格式是十六進制,,所以讀取的時候也應(yīng)該以十六進制的形式讀出。

第二:要保證文件中數(shù)據(jù)的個數(shù)和設(shè)定的讀取的數(shù)目(這里是256)保持一致,。例如,,要將生成文件data_out.txt中多余的換行符去掉(一般后會多出一行),否則Matlab會將空的行也當(dāng)做一個數(shù)據(jù),,從而兩個數(shù)目不一致,,導(dǎo)致Matlab報錯。

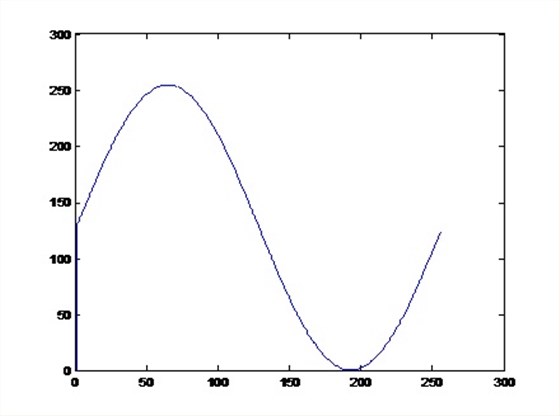

下圖是Matlab將data_out.txt中的數(shù)據(jù)讀出,,并顯示出的波形:

當(dāng)然,,有了Matlab這個強大的工具,也就可以很方便的看信號的頻譜等信息了,。

另外在說一點,,就是關(guān)于通過Verilog將數(shù)據(jù)寫入文件有多種方法,上面用的是$fdisplay這個系統(tǒng)函數(shù),,當(dāng)然還有$fmonitor和$fwrite等幾個命令,,下面簡單說一下這幾個命令的不同。

•$fdisplay

這個命令需要有觸發(fā)條件,才會把數(shù)據(jù)寫入文件,,例如,,上例的觸發(fā)條件就是always(i),當(dāng)i變化的時候才寫入,。每寫入一次數(shù)據(jù)會自動增加一個換行符,。

•$fmonitor

這個命令不需要觸發(fā)條件,只要有變化就可以將數(shù)據(jù)寫入文件,。例如可以通過以下語句:

initial $fmonitor(w_file,"%h",data_out);

這樣可以將整個仿真過程產(chǎn)生的data_out數(shù)據(jù)都寫入文件中,。

•$fwrite

這個命令和$fdisplay基本相同,也是需要觸發(fā)條件才會寫入,,不同的是每寫入一個數(shù)據(jù)不會自動添加換行符,。例如可以通過以下語句:

always @(posedge clk)

begin

$fwrite(w_file,"%h\n",data_out);

end

關(guān)于這幾個命令的詳細(xì)介紹,大家可以參考Verilog的相關(guān)數(shù)據(jù),。

簡單總結(jié)一下上面用到的幾個函數(shù):

•關(guān)于Matlab的函數(shù)有:fopen,, fscanf,fclose,。

•關(guān)于Modelsim的函數(shù)有:$fopen,, $fclose,$readmemh,,$readmemb,$fmonitor,,$fdisplay,,$fwrite。

上面就是我關(guān)于Matlab和Modesim進行聯(lián)合仿真的一些心得,,如果大家還有其他更好的方法,,希望不吝賜教啊,!

若您有高速數(shù)據(jù)采集板卡定制需求,,請聯(lián)系我們:400-000-4026

關(guān)于坤馳科技:

坤馳科技是專注于高速數(shù)據(jù)采集與信號處理、高速數(shù)據(jù)存儲與記錄的高科技公司,。坤馳科技為用戶提供成熟的標(biāo)準(zhǔn)高速數(shù)據(jù)采集產(chǎn)品與技術(shù),,也可為用戶提供定制化的高速信號采集解決方案。目前坤馳科技服務(wù)過的研究所,、科研單位已達近百家,。高速數(shù)據(jù)采集產(chǎn)品線涵蓋PCIExpress、cPCI,、PXIe,、VPX、USB等總線,包含高速AD,、DA平臺,、FPGA、DSP處理平臺,,SATA/SSD,、Flash存儲平臺等。

全國咨詢電話:400-000-4026

公司官方網(wǎng)站:http://www.jtyykv.cn

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關(guān)于坤馳

關(guān)于坤馳