以往要想以14bit分辨率,、2GS/s的速度檢測微弱脈沖信號,是無法實現(xiàn)的,現(xiàn)在北京坤馳科技有限公司的ADQ14系列數(shù)據(jù)采集卡結(jié)合行業(yè)領先,、自身專有的降低噪聲技術開發(fā)了相關的高級時域固件(ATD),實現(xiàn)了以上快速,、高分辨率的微弱脈沖信號檢測功能,。該脈沖數(shù)據(jù)采集系統(tǒng)包含以下核心內(nèi)容:

·用于脈沖數(shù)據(jù)線性識別的濾波函數(shù)

·用于噪聲非線性抑制的閾值運算函數(shù)

·通過重復測量計算波形平均抑制噪聲

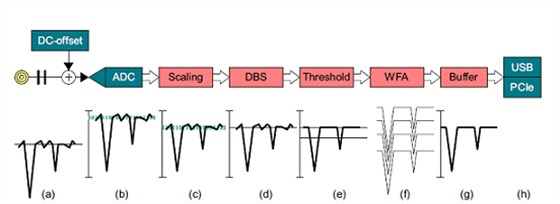

1,工作原理

高級時域固件的應用目的是加強用于脈沖測量的高速數(shù)據(jù)采集卡的信噪比,。固件包含一個基線調(diào)節(jié)器,、三個噪聲抑制級別、線性濾波,、非線性閾值,、能夠降低噪聲的重復測量波形平均功能。

ADQ14系列高速數(shù)據(jù)采集卡的每個通道都配置有一個高級時域固件(ATD)單元,,在相同的波形尺寸和累積數(shù)量設置下,,同步工作。每通道的閾值是獨立設置的,。

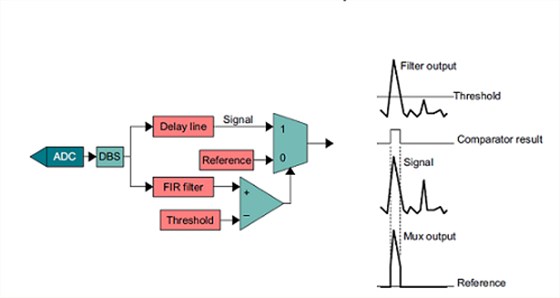

每通道高級時域固件的原理圖如下:

圖1

上圖的相關信號解釋及設置函數(shù)見下表:

2,,模擬輸入

如圖1(a),輸入模擬信號為單極性,這意味著信號相對于一個DC值基線和一個信號脈沖構(gòu)建的,。信號的DC值不必為0,,一些DC耦合的高速數(shù)據(jù)采集卡,將使得輸入信號的直流電平高于0點,,如果需要,,AC耦合版本,可以移動輸入DC電壓值,。

一個模擬的DC偏置加到信號中,,可實現(xiàn)ADC的對稱輸入范圍充分使用。這將使信號基線接近信號范圍的上限或下限,。峰值波形能覆蓋所有信號范圍,。直流偏置有效的加倍了單極信號的分辨率。如圖1(b).直流偏置(DC-offset)電壓由軟件控制,,控制范圍為電壓上限到下限,,但好留有10%的范圍,,以適應信號過沖。

3,,零電位調(diào)準和信號縮放

當為了獲取理想電壓范圍使用直流偏置(DC-offset),,基線接近信號一端,如果需要,,可使用數(shù)字化增益和偏置調(diào)整模塊來縮放信號,。

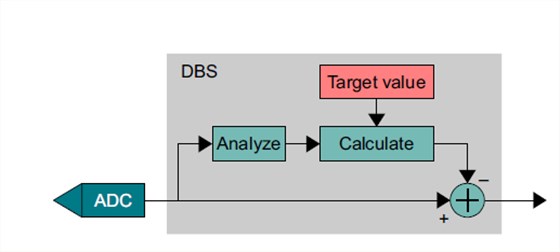

4,數(shù)字基線穩(wěn)定器,,DBS

對于常見的直接信號分析,,模擬的直流電平(DC-level)是準確的,然而,為得到非線性閾值操作的佳性能,,基線應該鎖定為一個確定值,。本處由數(shù)字基線穩(wěn)定器(DBS)實現(xiàn),其配置在A/D轉(zhuǎn)換器之后。DBS是SP devices的一項專利技術,,通過分析數(shù)據(jù),、找到和調(diào)整基線為22位精度的目標值。如圖2.

目標值由使用者設定,,好接近模擬增益(DC-offset),,如果應用了DC-offset這一功能。DBS應用了模糊識別的方法進行數(shù)據(jù)處理,,DBS是一直激活的,,其不斷的監(jiān)視和跟隨基線變化,并矯正基線為時不變值,。

圖2

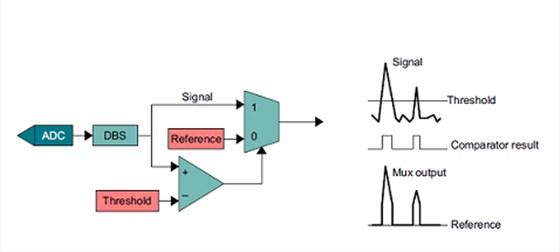

5,,高級閾值設置

5.1 概述

閾值功能基于以下幾個基本模型(依據(jù)單極性脈沖的極性),如圖3.

·對于采集系統(tǒng)的正脈沖,,采樣低于閾值(設置的參考值)

·對于采集系統(tǒng)的負電壓,,采樣高于閾值(設置的參考值)

處理結(jié)果為,與閾值相等信號和低于閾值的信號被視為噪聲被移除,。

圖3 正脈沖的基本閾值操作

5.2 利用濾波器的線性噪聲抑制

當脈沖具有可以與本底噪聲分離的性質(zhì)時,,濾波功能就可以用來加強信號特性,之后性噪比會提高,,閾值精度也會提高,。濾波器通常為形狀相關的,使用濾波或相關功能時,,脈沖由多個樣本復現(xiàn)出來,。

例如:低通濾波器將辨別噪聲的高頻部分,因此降低噪聲的峰值幅度。

例如:對弱脈沖的形狀已經(jīng)初步了解時,,使用濾波器相關到其形狀,,以放大這類有用形狀,壓縮其他形狀,,也就是壓縮噪聲。

注意到,,濾波器僅對選擇的處理過程起作用,,輸出數(shù)據(jù)并不濾波。

5.3 應用閾值

原理如圖4所示,,噪聲抑制的非線性部分,,原理是使得認為是信號得部分為大幅度,噪聲部分為小幅度,。

在脈沖能夠識別的位置,,閾值應用到濾波信號,高于閾值的原始信號極其位置會保存下來,。注意到閾值應用到濾波信號,,因此原始非濾波信號數(shù)據(jù)為輸出數(shù)據(jù),這是為了保留原始信號波形形狀,,圖中的延遲線(delay line)用來匹配分支運行時間,。

沒有脈沖的位置被寄存器R的存儲值代替,寄存器R存儲值與DBS的目標值相同,。

圖4 數(shù)據(jù)流。濾波信號用于選擇采樣位置,,原始信號用于結(jié)果輸出

5.4 準確度

閾值精度由DBS的準確度決定,,22bits。通常,,DBS將依據(jù)22bits時的測量誤差調(diào)整基線值為14位整數(shù),,閾值和參考值為相同數(shù)據(jù)格式時,沒有舍入誤差,。

6 ,,波形平均

6.1 累加數(shù)據(jù)字

波形平均是利用累加器將波形相加后求平均,每個波形的個樣本加到其他波形的個樣本,,每個波形樣本都有相同的長度,,每個數(shù)據(jù)字的尺寸為32bits,因此,輸入14bits數(shù)據(jù)高有效位(MSB)對齊到16bits字,。有16位的可用空間用于存儲附加信息,。這意味著硬盤數(shù)據(jù)溢出之前,可存入2^16=65536個波形數(shù)據(jù)。波形平均功能包括針對波形數(shù)目的除法,,然而,,這個除法不能適用于FPGA,需由用戶軟件操作完成,。

6.2 累加矢量長度

波形平均使用板上DRAM作為累加器,。波形數(shù)可以很大,多5Msamples,。

6.3觸發(fā)

每個波形都由觸發(fā)啟動,,所有的采樣觸發(fā)都可選為波形觸發(fā)。系統(tǒng)波形平均更好的利用了重復測量功能,,觸發(fā)可以是來自于與外部觸發(fā)源的外部觸發(fā)也可以是內(nèi)部觸發(fā),。通常,脈沖形狀可以分析,,觸發(fā)電平用于多次觸發(fā)重復脈沖,。

每個波形結(jié)束后的空載時間為20ns,為上一次采樣結(jié)束到系統(tǒng)接收新的觸發(fā)的時間間隔。

7,, 數(shù)據(jù)讀出到主機

由于數(shù)據(jù)讀出到主機的速度小于數(shù)據(jù)采集的速度,,板上必須有一個額外的緩沖空間在波形數(shù)據(jù)發(fā)送到主機之前存儲波形。經(jīng)由累加器的波形平均后,,PC數(shù)據(jù)率的需求是降低很多的,。但當后一個波形被累加后,一段時間內(nèi),,累加器為數(shù)據(jù)讀出封鎖并不再接收新的波形,。ADQ14通過引入一個外加的緩沖區(qū)(buffer),在數(shù)據(jù)讀出之前保存結(jié)果,同時不封鎖累加器,。一個新的累加過程將于20ns后啟動,。

8 ,仿真結(jié)果

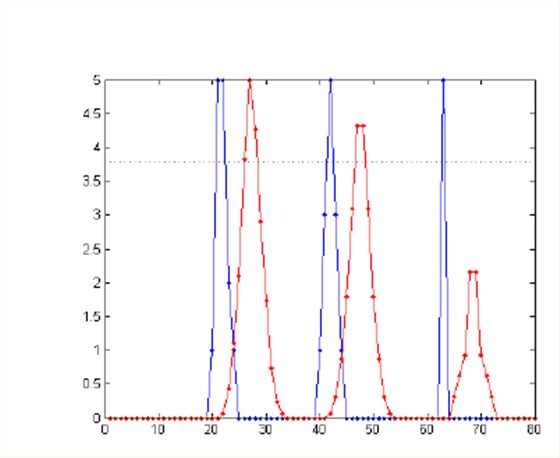

圖5中顯示了相對于同一采樣時鐘不同相位的脈沖信號,,藍色信號帶有尖峰噪聲,。紅色信號為濾波后的結(jié)果。這里的關鍵是信號脈沖波形大于一個采樣寬度,,噪聲波形小于一個采樣寬度,,這是典型的高斯噪聲。

圖5

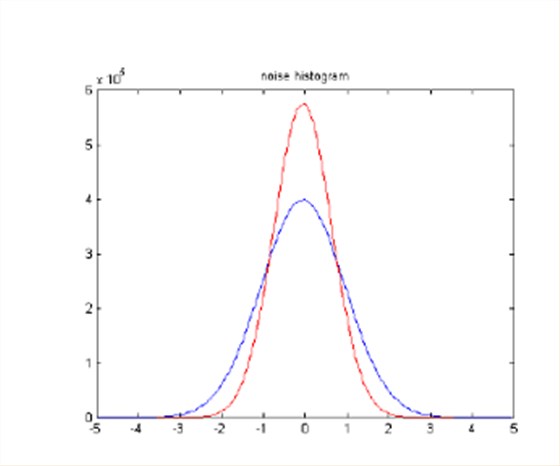

圖6顯示了來自于圖5的兩列脈沖和高斯尖峰噪聲,,藍色曲線為濾波前,,紅色為濾波后。底部紅色曲線來自基于閾值的原始信號濾波后的閾值濾波噪聲,。圖7為濾波前后的噪聲直方圖,,濾波后,,噪聲幅度降低。

圖6 濾波前后的兩列脈沖和隨機噪聲尖峰

圖7 濾波前后的噪聲直方圖

9,, 并行采樣處理

FPGA 的數(shù)據(jù)率僅為250MHz,因此,,高速數(shù)據(jù)采集時,采樣操作必須為并行處理,,這會給一些尺寸設置帶來了約束條件,,例如,匹配信號路徑到濾波器的延遲時間設置為8個步長,,為了微調(diào)各個操作分支的時間,,濾波器峰值的位置可以移動一個采樣長度。

電話咨詢

電話咨詢 產(chǎn)品中心

產(chǎn)品中心 在線留言

在線留言 關于坤馳

關于坤馳