脈沖信號(hào)采集方案

基于PCIE總線的脈沖采集方案

一,、概述:

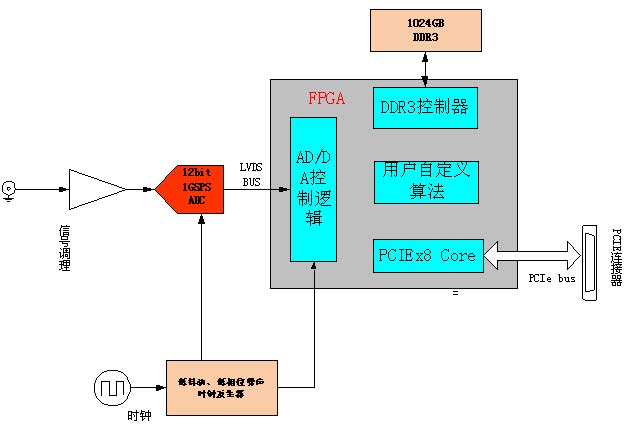

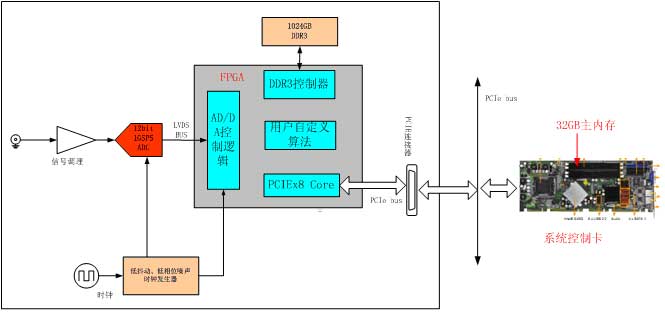

為采集高速脈沖輸入信號(hào),并能實(shí)施將采集數(shù)據(jù)傳入PC主內(nèi)存,,系統(tǒng)方案規(guī)格如下:

1.采用12bit1Gsps高速ADC,。

2.50歐姆阻抗輸入。直流藕合,,輸入信號(hào)范圍0~+5V,輸入模擬帶寬大于500MHz。

3.板載2GBDDR3內(nèi)存,。

4.采用PCIEx8接口。

5.支持用戶二次開(kāi)發(fā)FPGA邏輯,。

6.提供用戶二次開(kāi)發(fā)軟件,。

系統(tǒng)框圖如下:

二、為了實(shí)時(shí)得到采集數(shù)據(jù),,在數(shù)據(jù)傳輸端,,可以采用如下4種方案:

方案1:

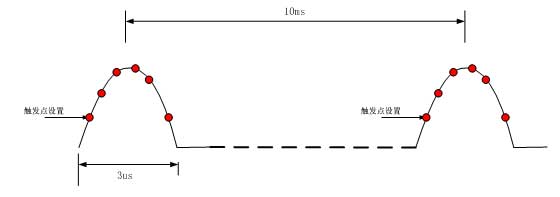

通過(guò)設(shè)置觸發(fā)門(mén)限,只采集有用信號(hào),。

在脈沖周期為10ms時(shí),,每個(gè)脈沖根據(jù)觸發(fā)設(shè)置,采集3us左右(長(zhǎng)度可以設(shè)置),,約3000個(gè)采樣點(diǎn),;實(shí)時(shí)傳輸數(shù)據(jù)率為600KB左右。通過(guò)PCIEGen1x8總線傳輸,,DMA傳輸率為1250MB/s,。

方案2:

如果需要實(shí)時(shí)傳輸采集數(shù)據(jù),12bitX1Gsps等于2GB/s,,需要采用PCIEGen2x8總線傳輸。PCIEGen2x8總線傳輸理論上支持3000MB/s的傳輸率,。

配合高性能計(jì)算機(jī),,配置32GB主內(nèi)存,,理論上可以將2000MB/s的數(shù)據(jù)實(shí)時(shí)傳輸?shù)接?jì)算機(jī)中,。

方案3:

該系統(tǒng)支持FPGA二次開(kāi)發(fā),用戶可以將算法通過(guò)FPGA實(shí)現(xiàn),。通過(guò)FPGA的實(shí)時(shí)信號(hào)處理,,數(shù)據(jù)率可以大大減小。

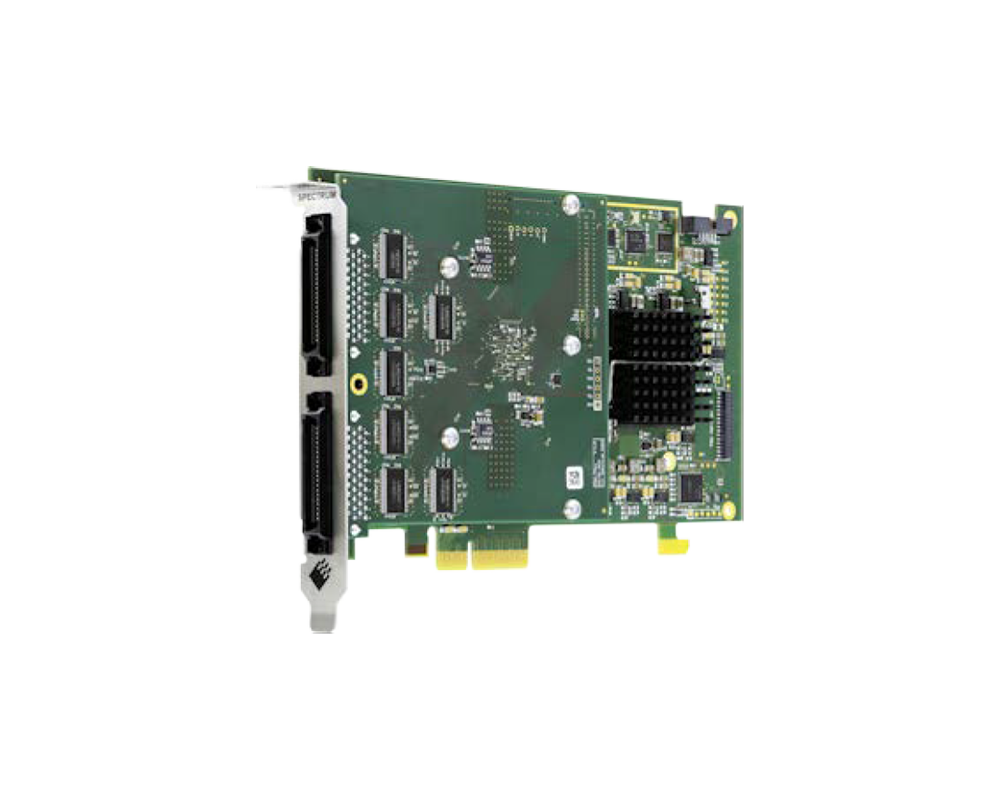

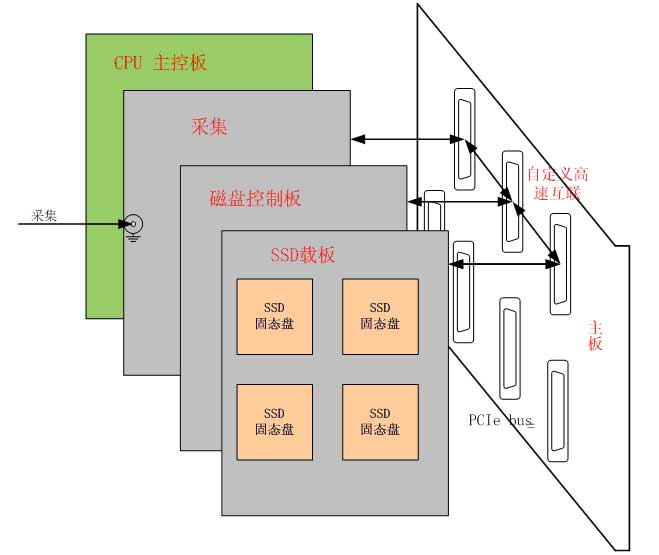

方案4:

在采集卡旁邊增加一塊PCIE板,,上面FPGA具有磁盤(pán)控制功能,,能在機(jī)箱上連接8-16塊SSD盤(pán),實(shí)時(shí)存儲(chǔ)速度大于2000MB/s,。由于SSD磁盤(pán)容量較大,,小容量256GB,大容量9.6TB,,存儲(chǔ)波形時(shí)間非常長(zhǎng),。

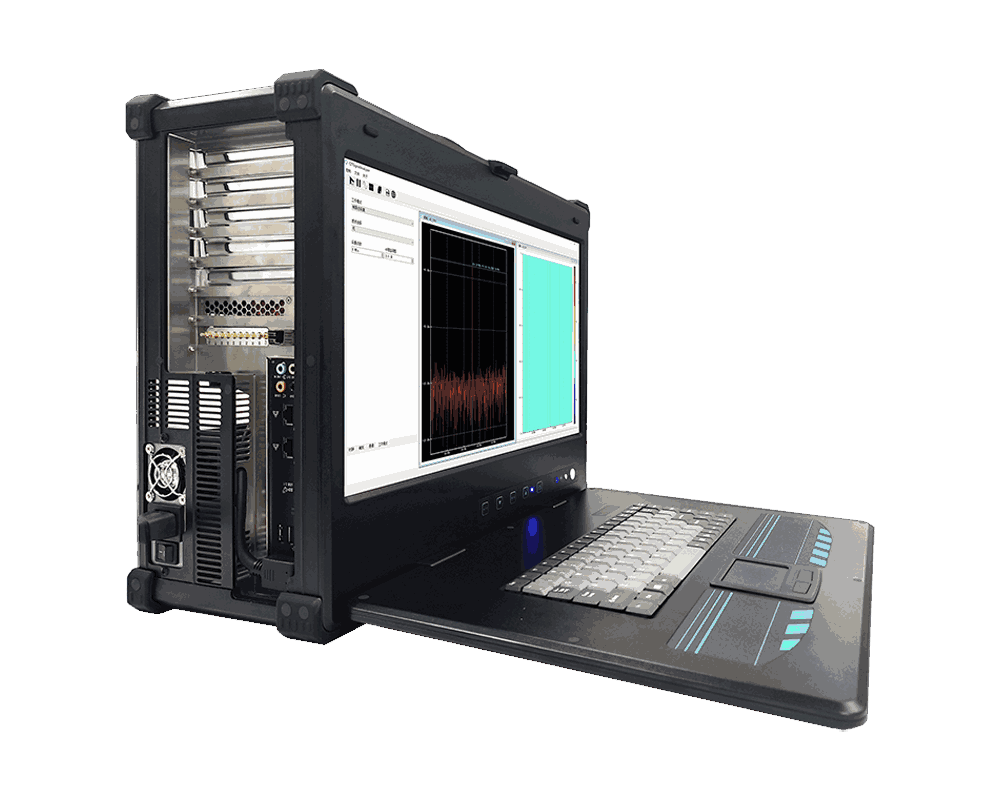

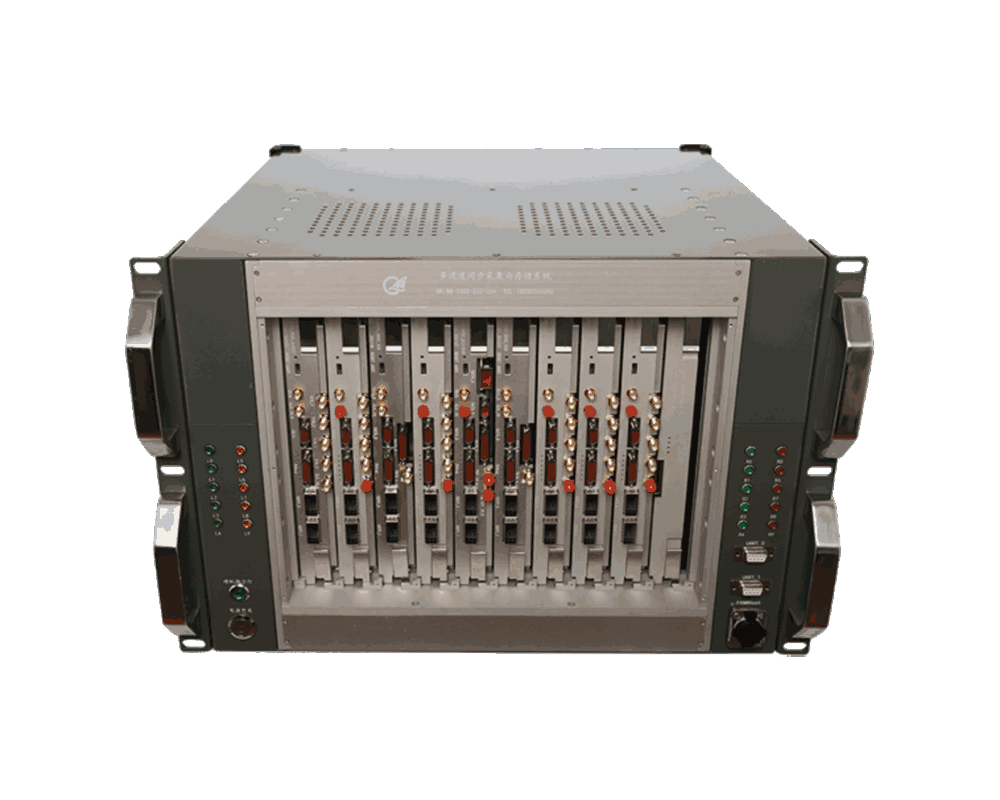

附圖為磁盤(pán)儲(chǔ)存樣機(jī):

方案對(duì)比表:

|

方案 |

技術(shù)準(zhǔn)備度 |

后期開(kāi)發(fā)工作量 |

成本 |

||

|

采集 |

FPGA |

PCIE總線 |

|||

|

只采集有用信號(hào) |

需開(kāi)發(fā) |

少量開(kāi)發(fā) |

PCIE Gen1 |

只需開(kāi)發(fā)算法 |

低 |

|

采集全部波形 |

需開(kāi)發(fā) |

少量開(kāi)發(fā) |

PCIE Gen2 |

只需開(kāi)發(fā)算法 |

高, 需要高性能FPGA和 |

|

FPGA實(shí)時(shí)計(jì)算 |

需開(kāi)發(fā) |

大量開(kāi)發(fā), |

PCIE Gen1 |

軟件工作量小,F(xiàn)PGA |

中,, FPGA開(kāi)發(fā)周期長(zhǎng) |

|

FPGA直接存儲(chǔ) |

需開(kāi)發(fā) |

少量開(kāi)發(fā), |

PCIE Gen1 |

軟件工作量小 |

高,, 需要格外增加一塊FPGA-PCIE卡,需要外接32塊SSD盤(pán) |

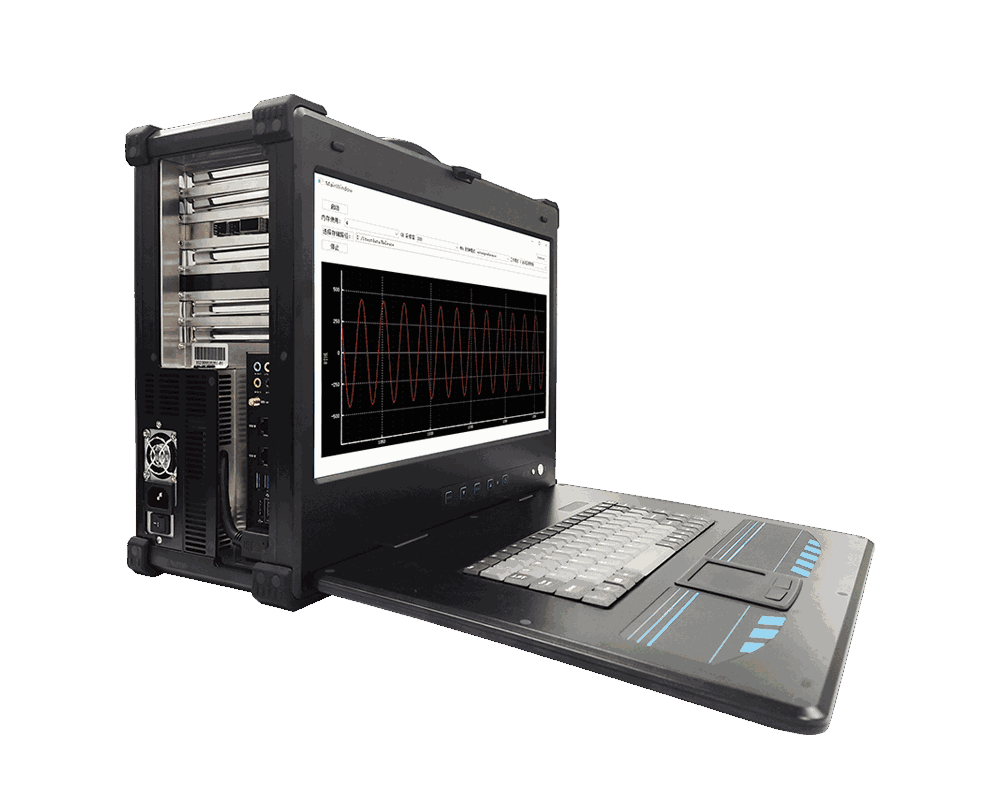

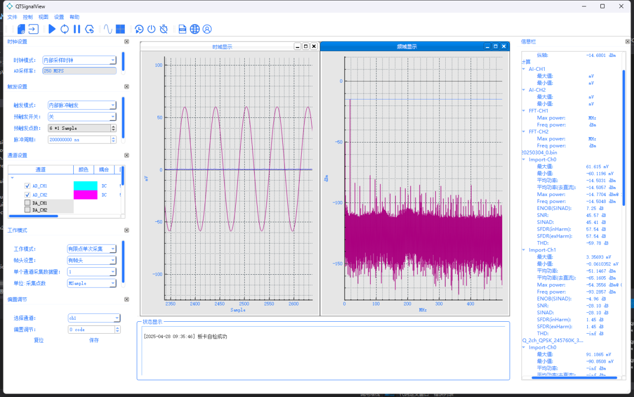

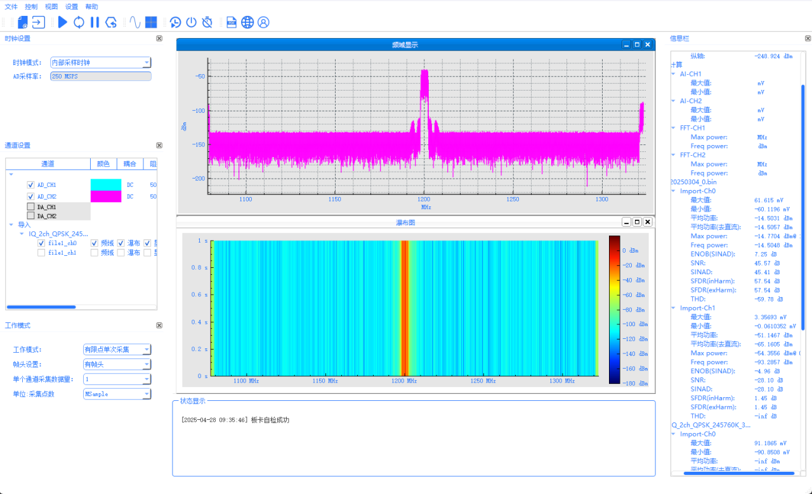

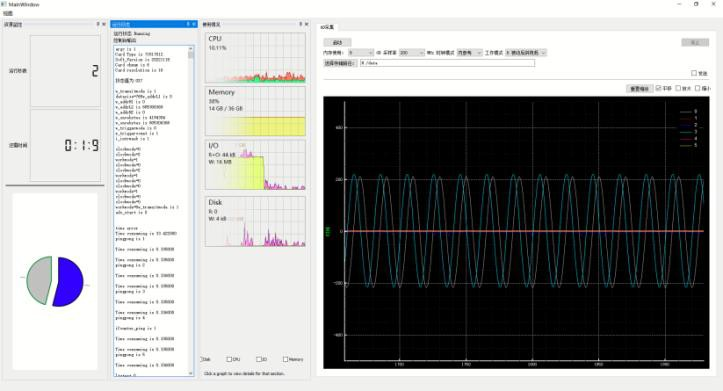

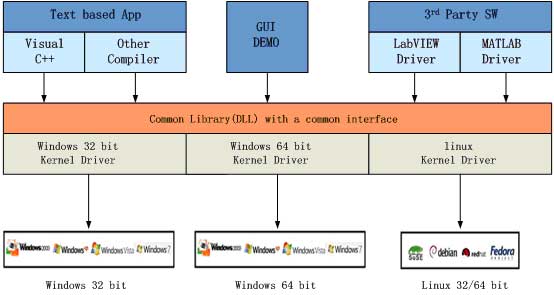

三,、系統(tǒng)應(yīng)用軟件如下:

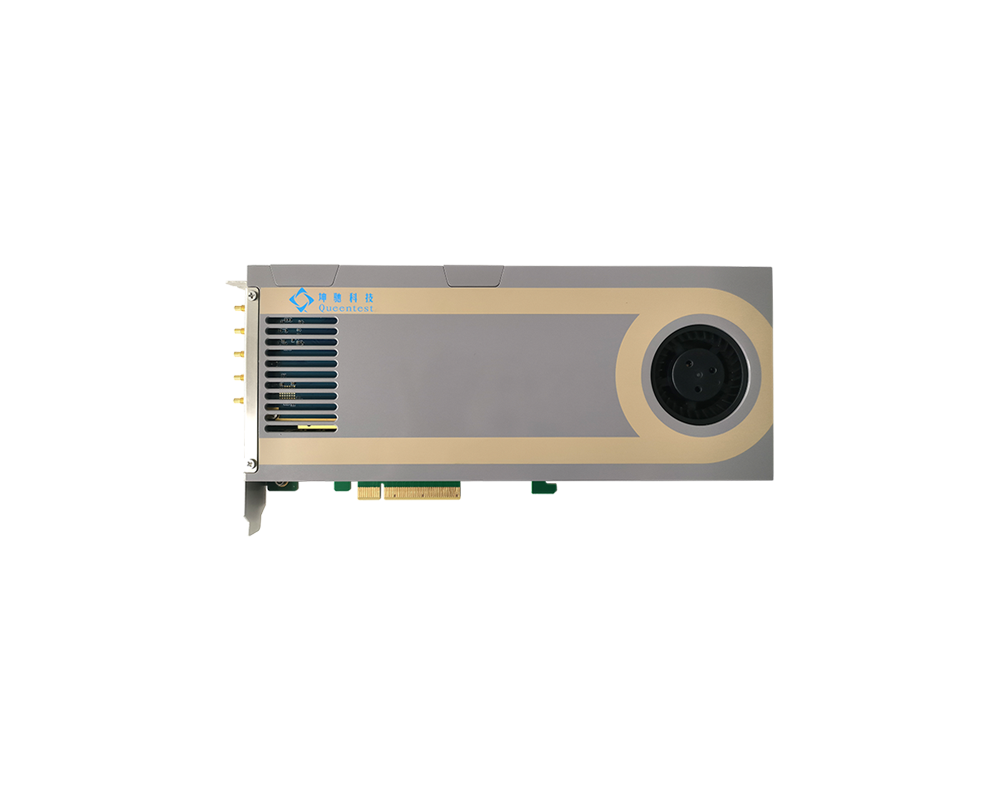

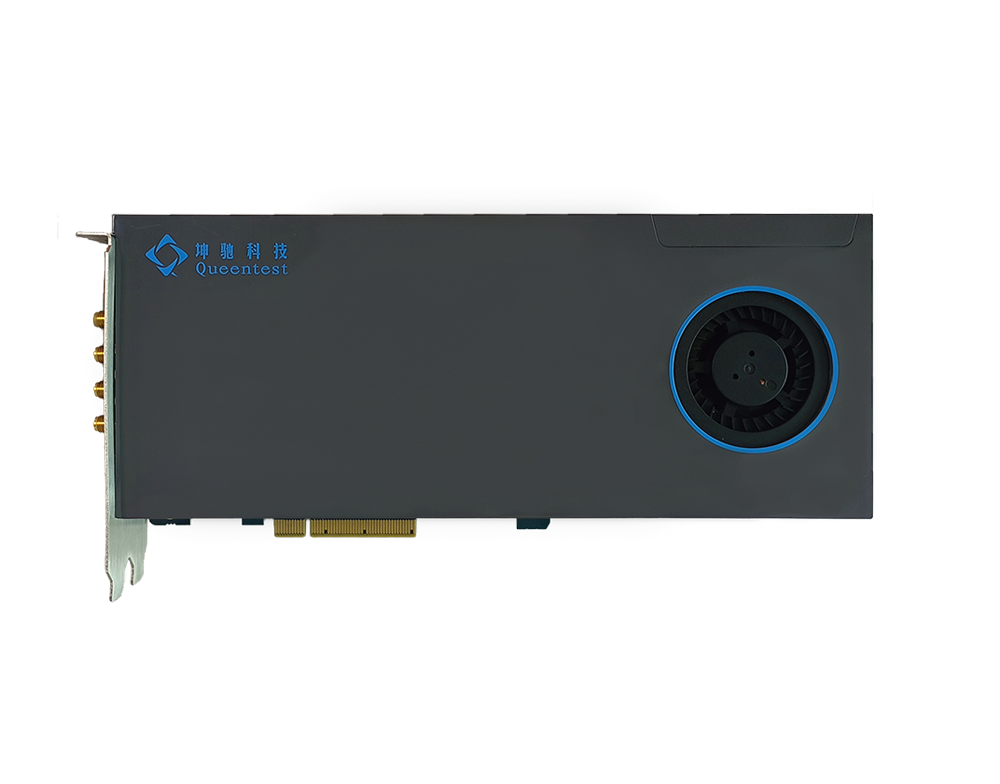

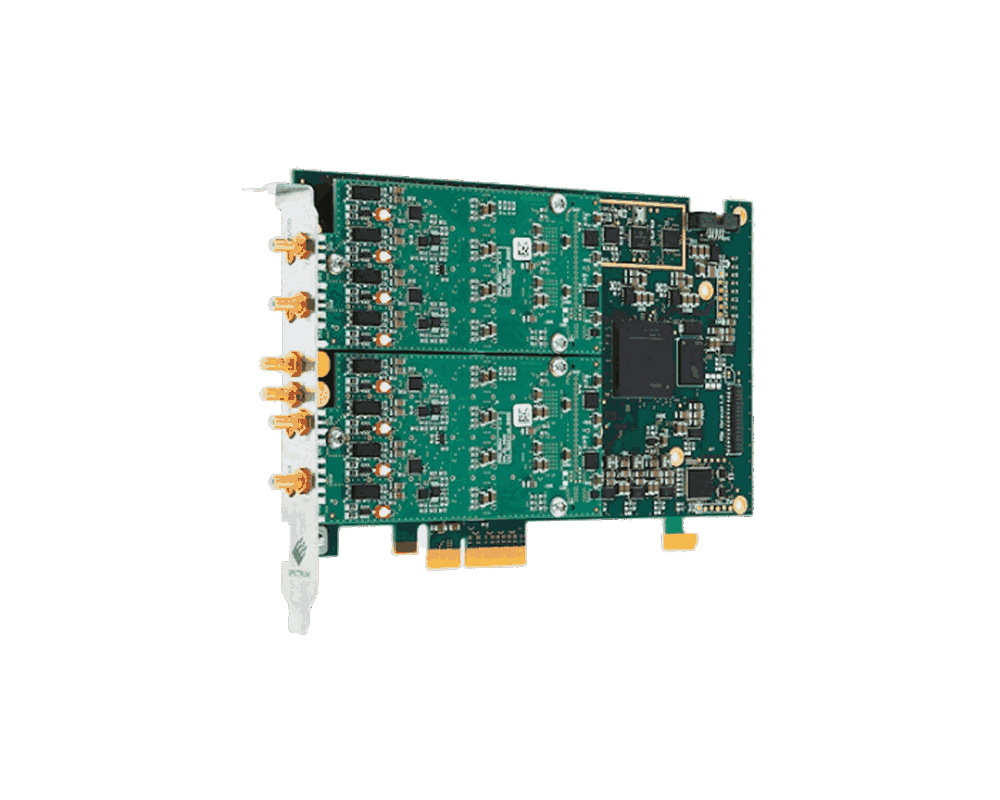

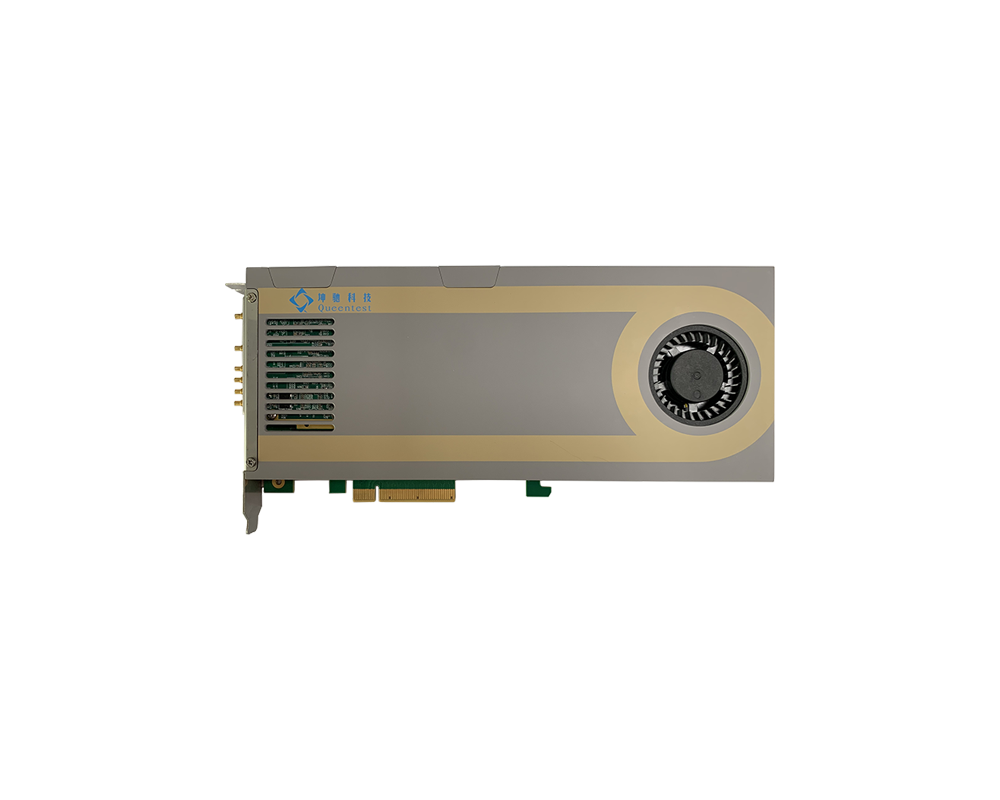

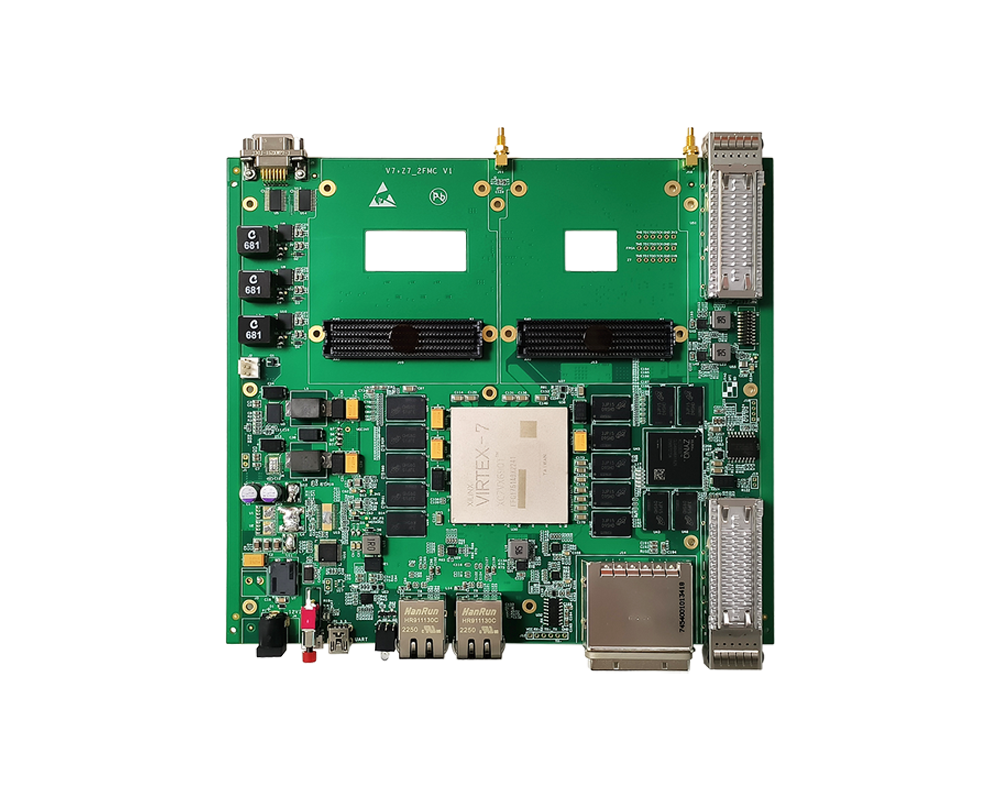

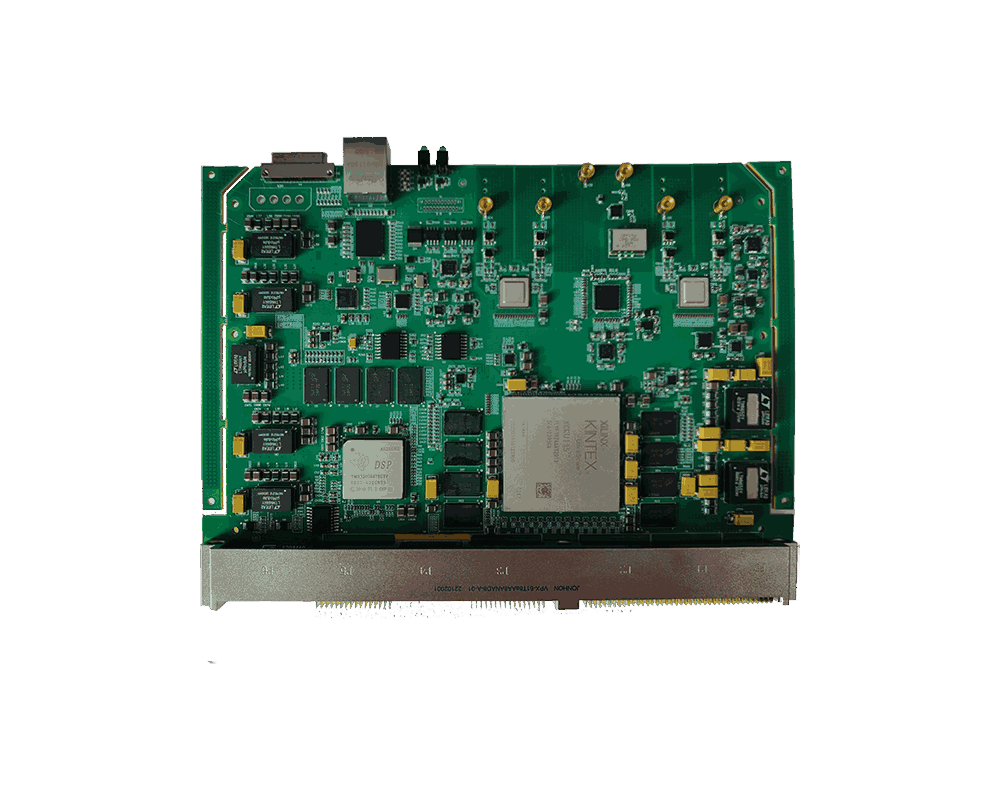

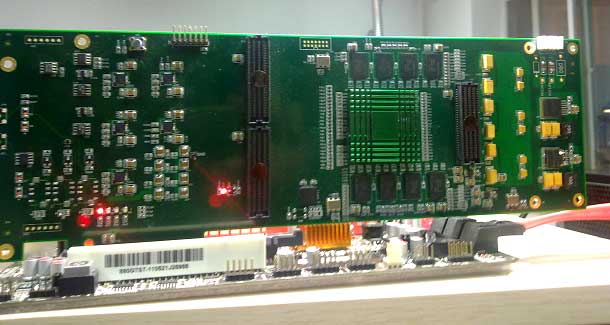

四,、PCIE采集卡實(shí)際圖如下:

-

M4i.44xx-PCIe總線直流耦合采集卡

PCIe×8 Gen2 接口;獨(dú)立ADC的雙通道或者四通道,;4通道,;130MS/S~500MS/s;14/16bit 數(shù)字化儀

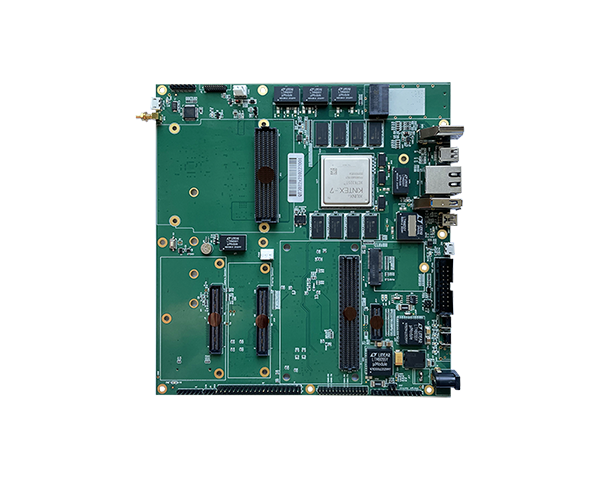

-

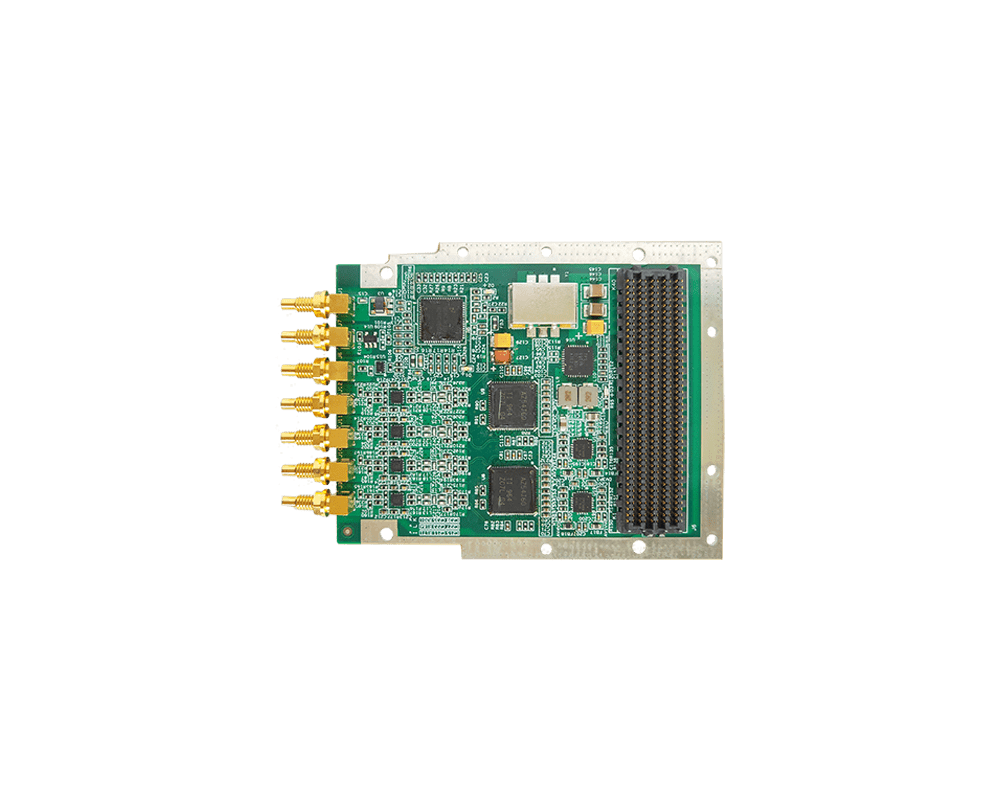

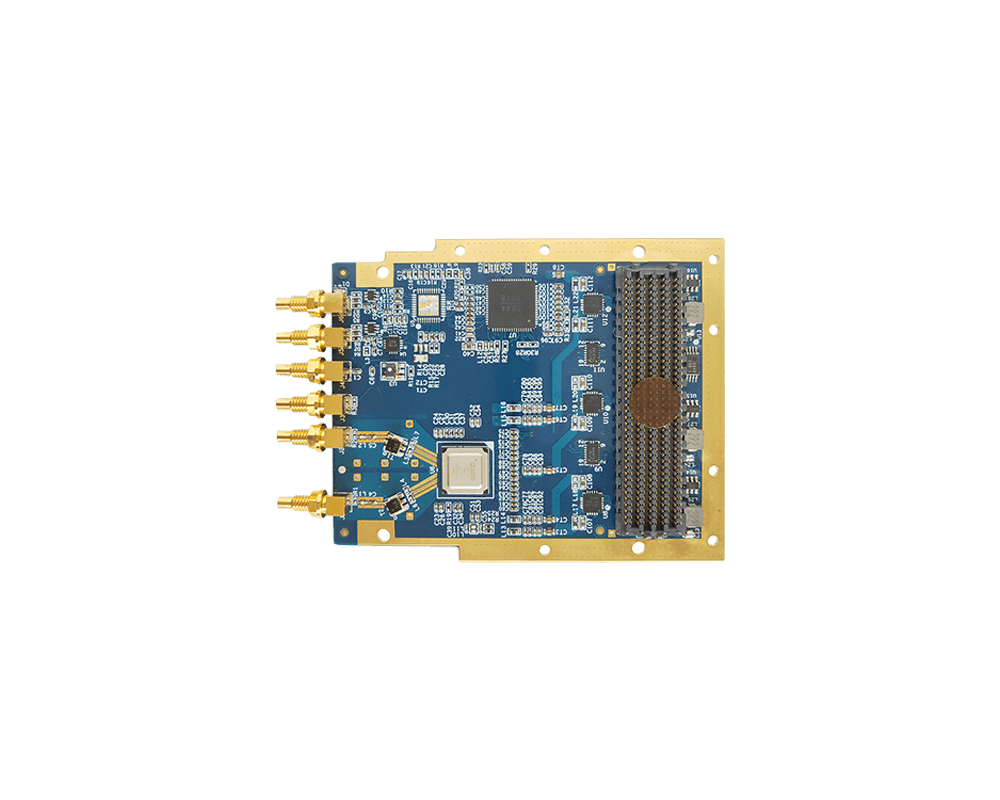

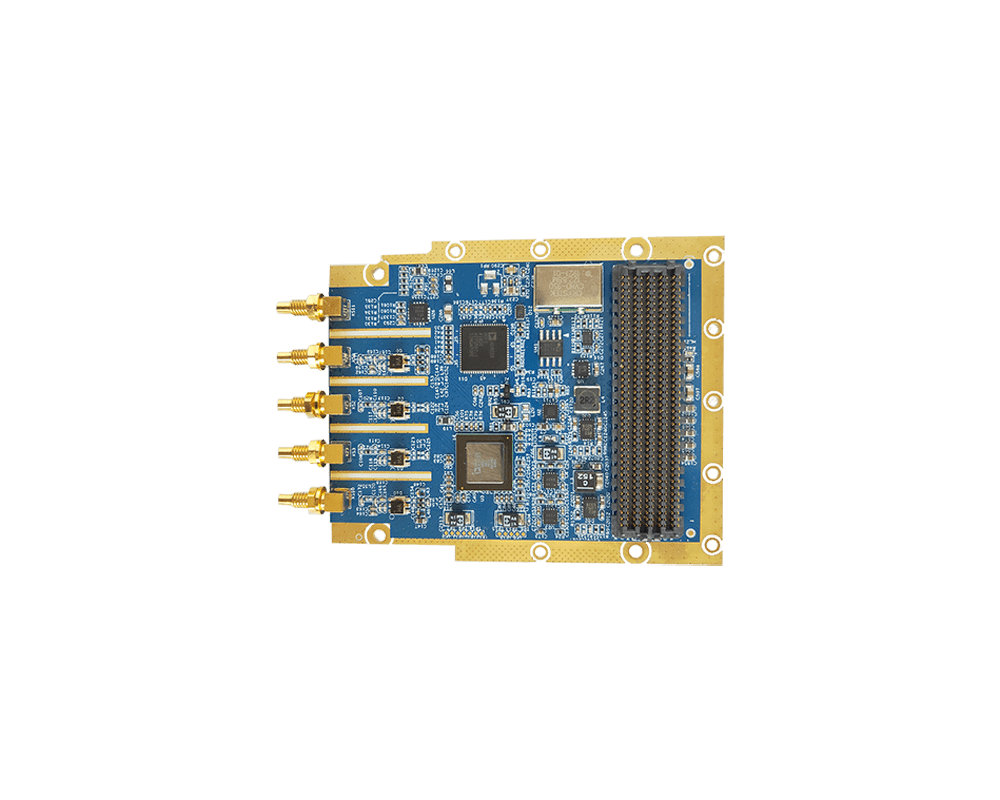

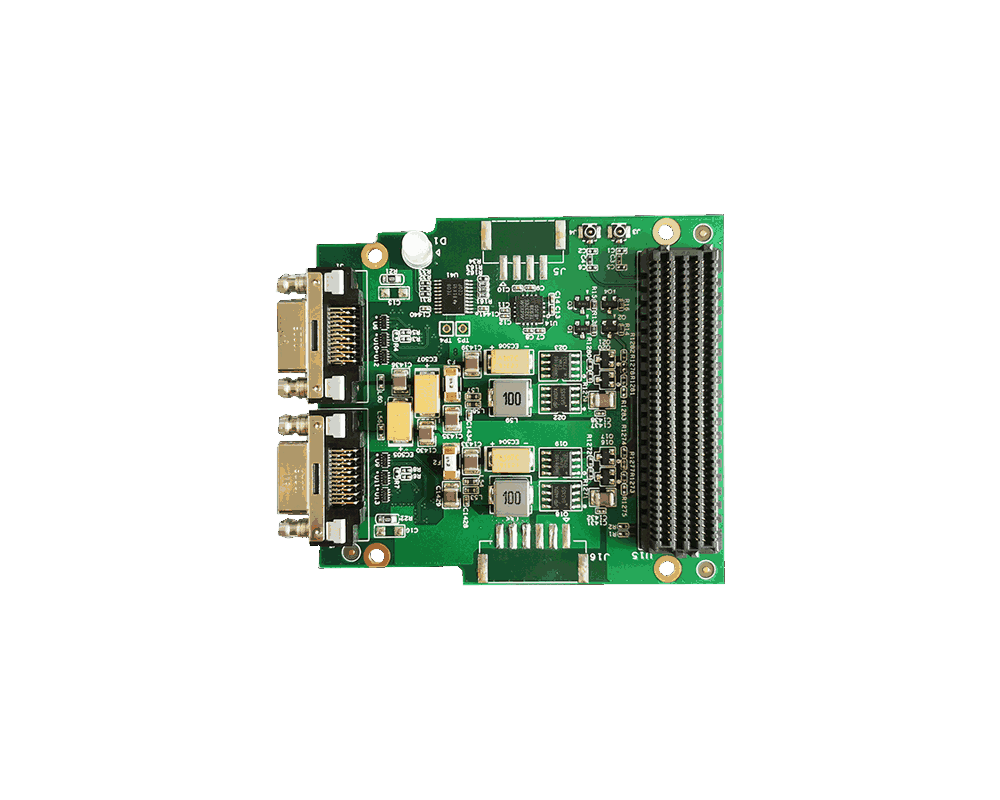

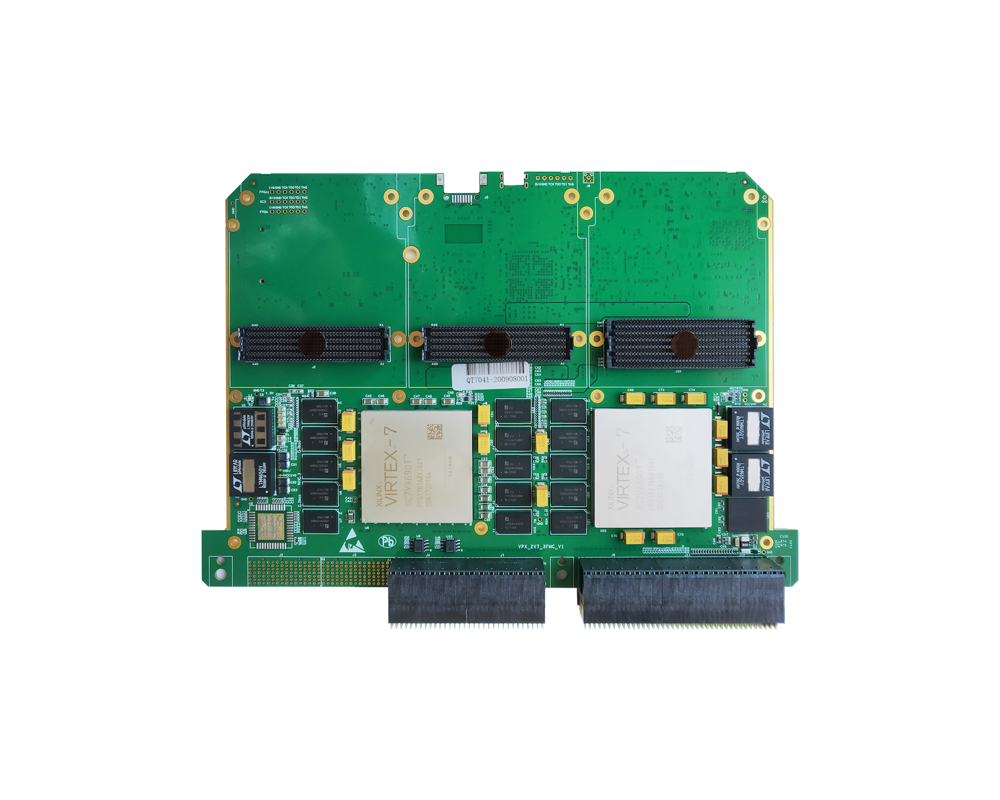

QT7022-光纖/以太網(wǎng)載板

基于K7和TX2的高性能FMC載板

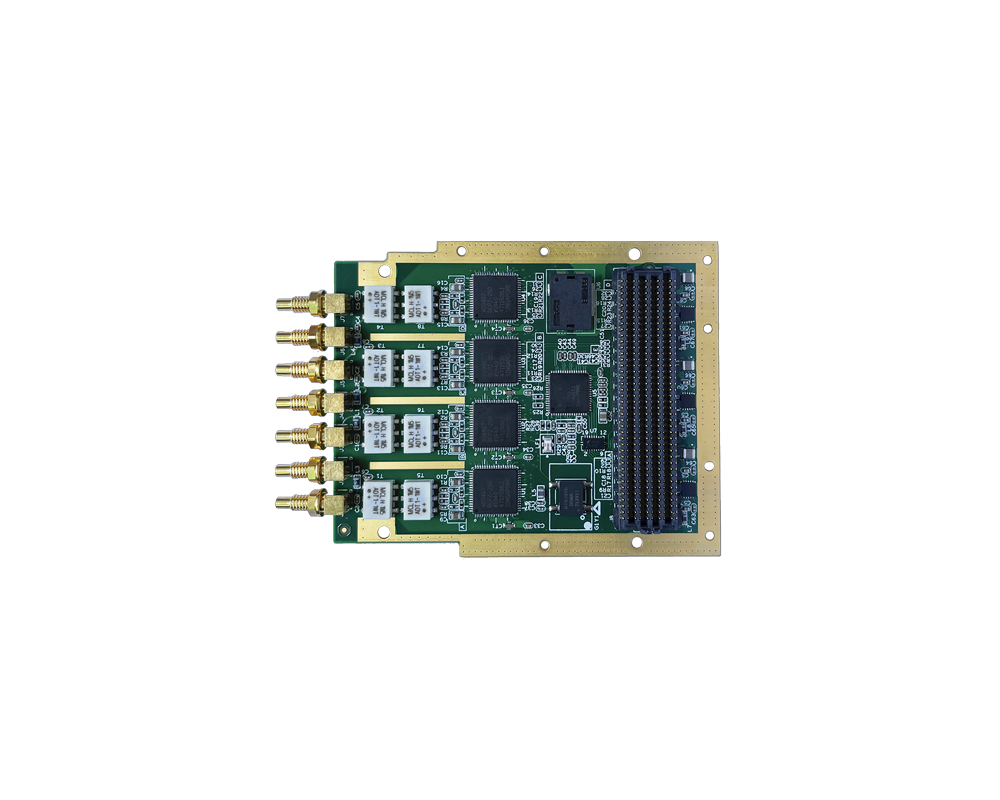

-

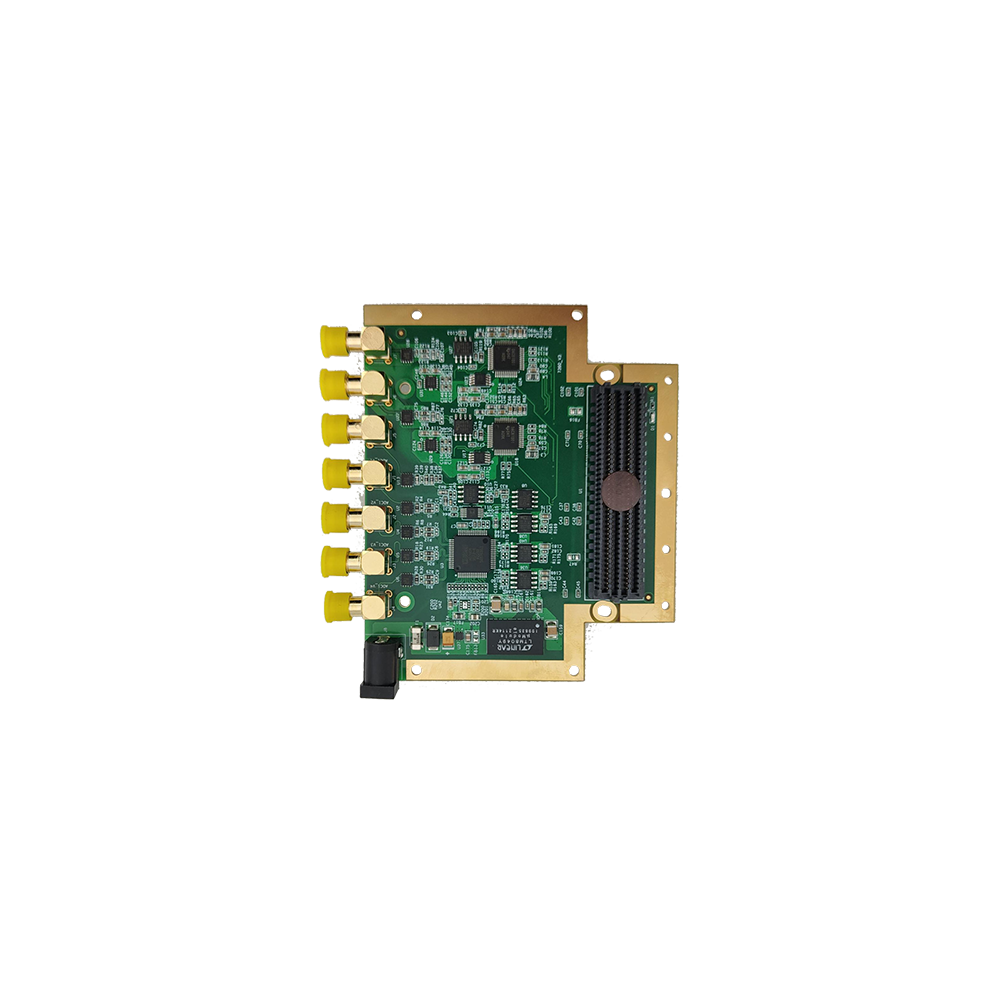

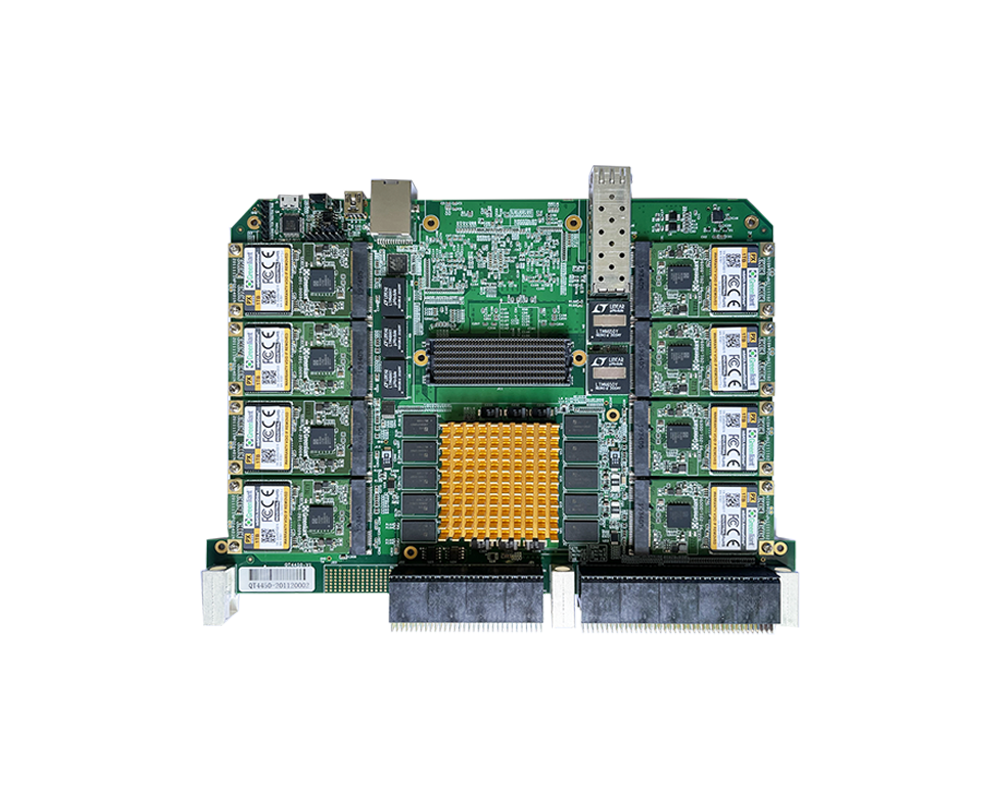

QT7150-FMC AD 子卡

數(shù)據(jù)量化16位,,有效分辨率>11.3,;4通道,250MS/s采樣率,;支持外部同步/觸發(fā)輸入和輸出

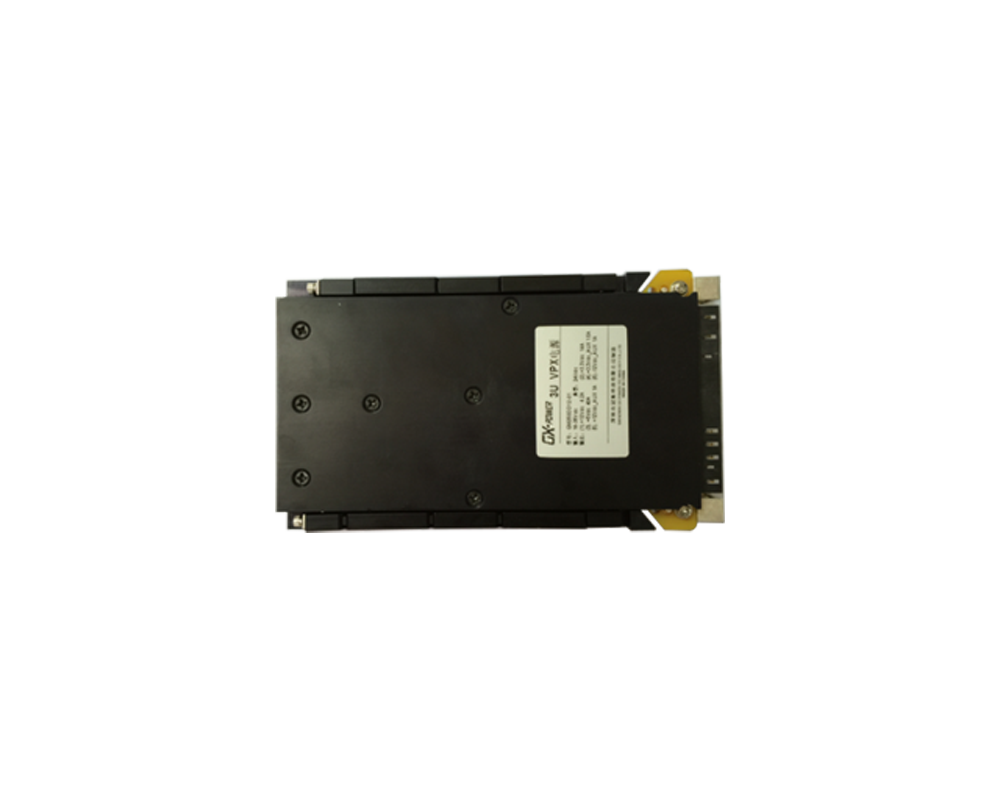

-

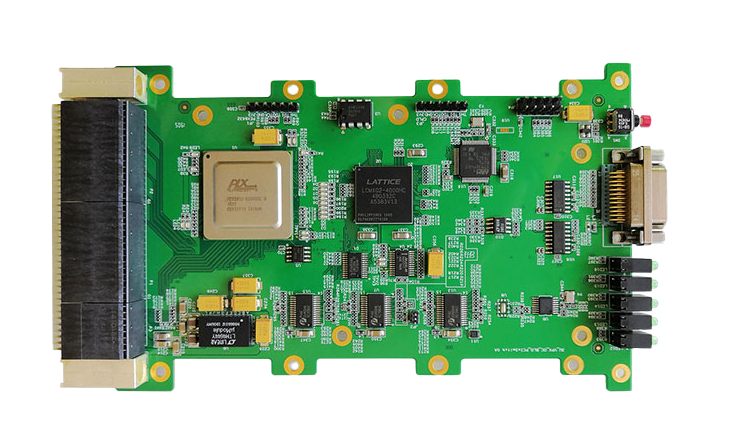

QT2012-3U VPX電源卡

標(biāo)準(zhǔn) 3U 尺寸,、標(biāo)準(zhǔn) VPX 電源連接器 整個(gè)電源系統(tǒng)具有很高的可靠性 具有寬范圍的 DC 輸入范圍,四路 DC 輸出 直流輸入 26 - 60Vdc