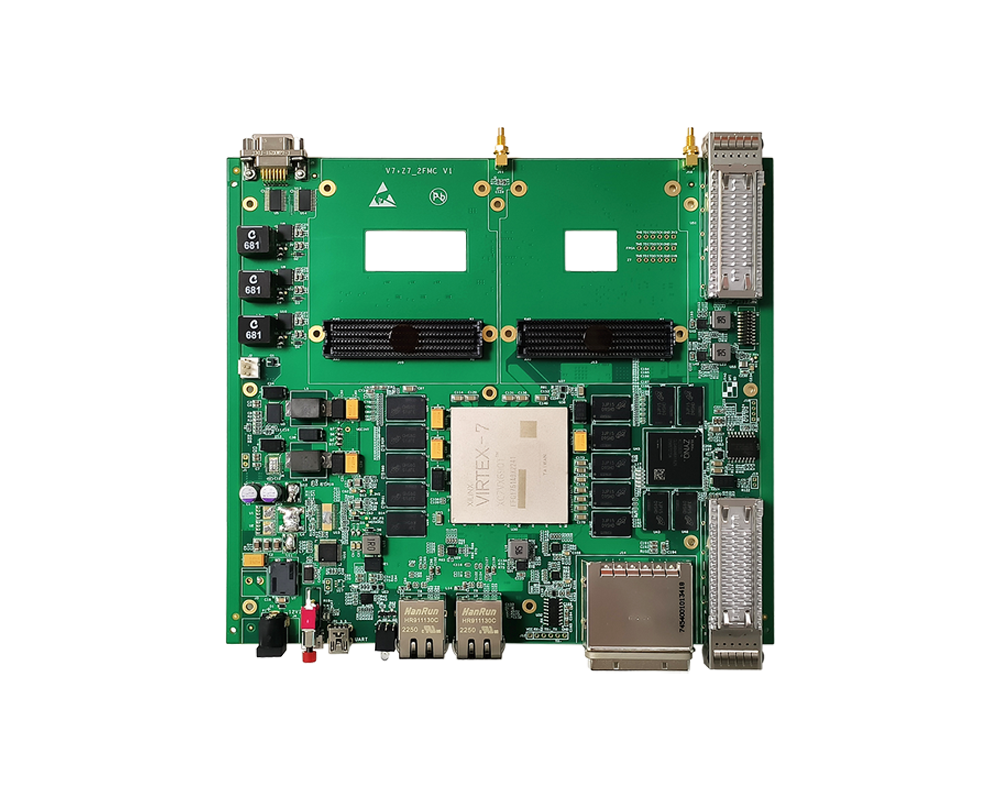

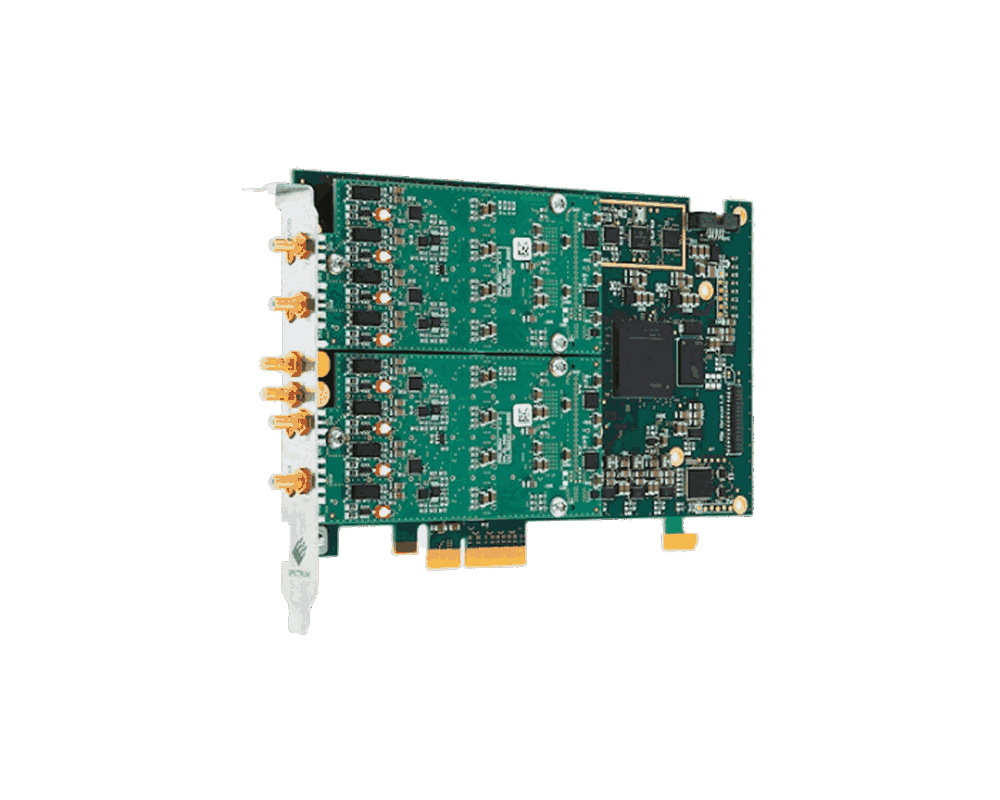

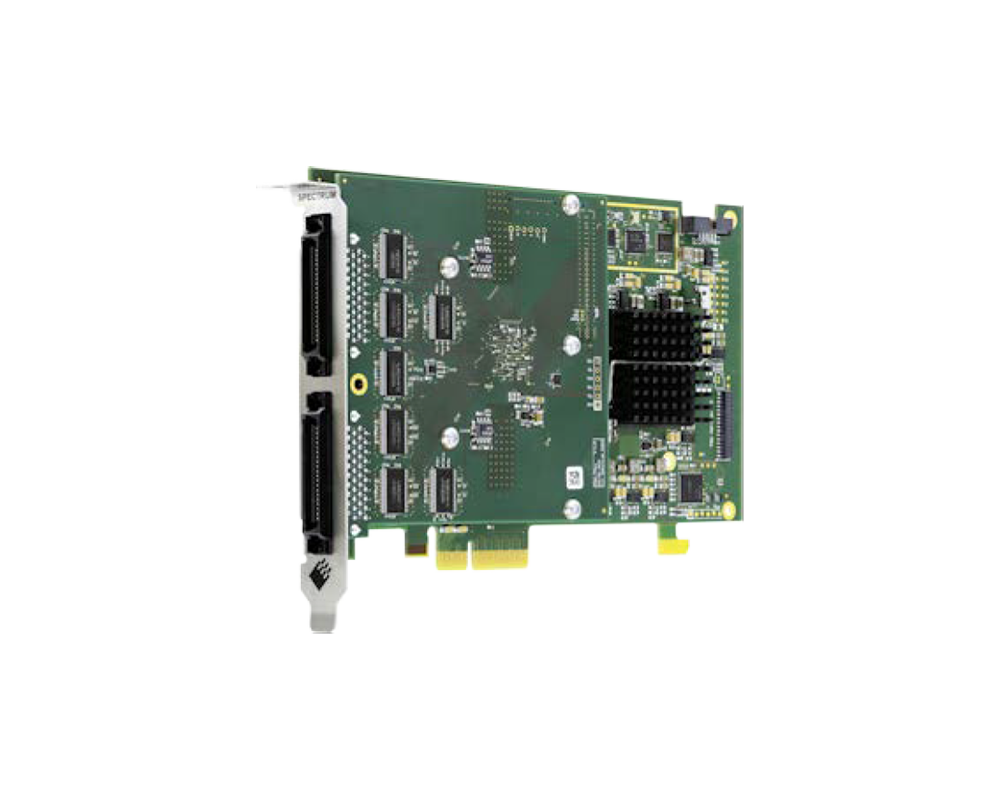

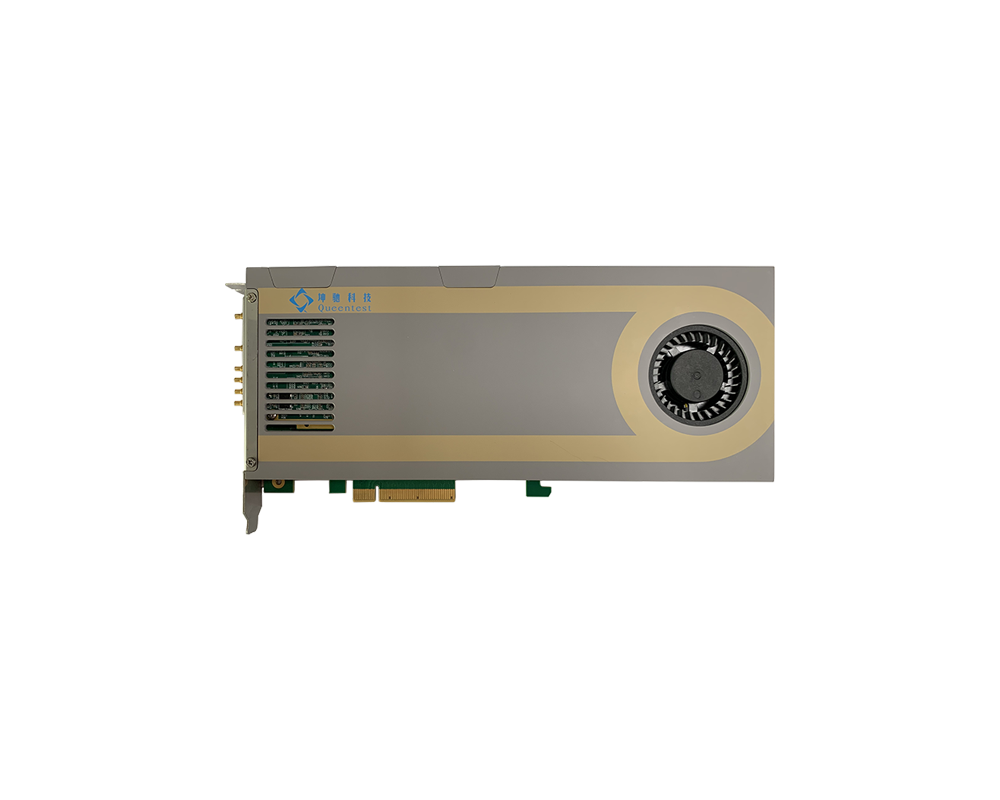

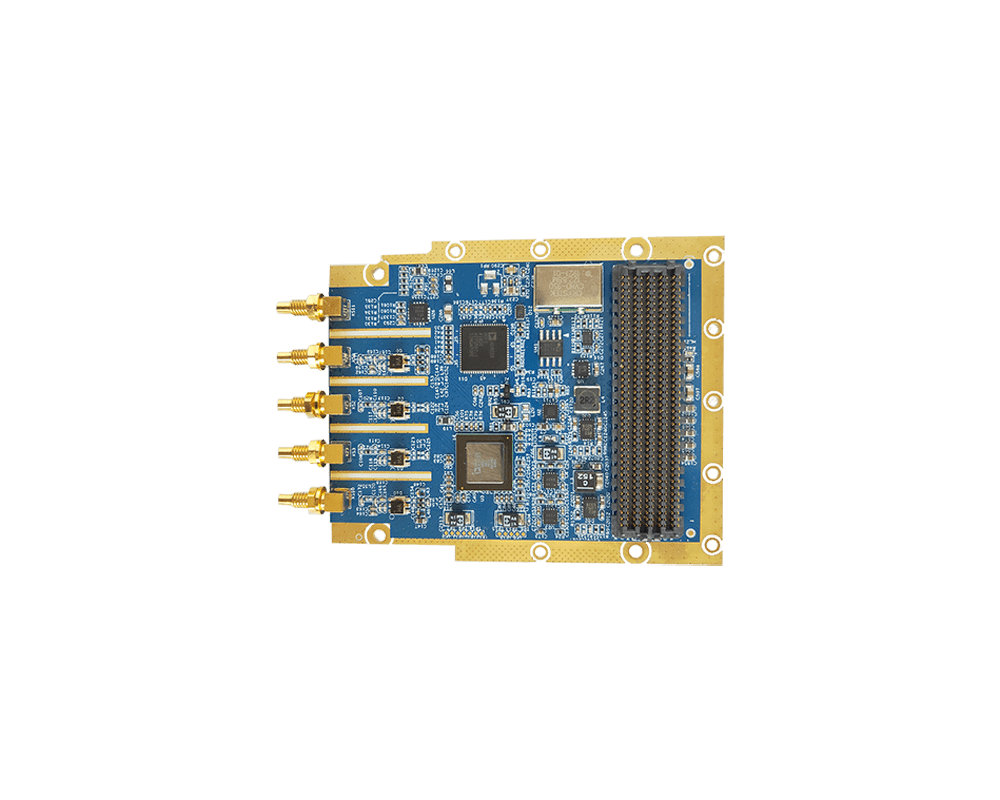

數(shù)字IO卡是采集數(shù)字IO信號的儀器,其功能類似于邏輯分析儀。北京坤馳科技公司的M2i.7011數(shù)字IO卡有16,、32與64bit版本可選,且在16bit與32bit版本中高采樣率可達125MS/s,。板卡具備高2GB板載內(nèi)存,在FIFO下,,板卡持續(xù)流模式傳輸速度可達160MS/s,,可滿足大部分使用需求。

在本次應(yīng)用實驗中經(jīng)過對過程中問題的分析,、解決,,實現(xiàn)了對藍牙信號的采集。

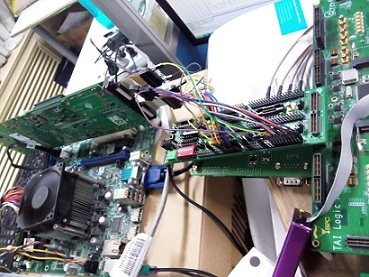

1 environment setup

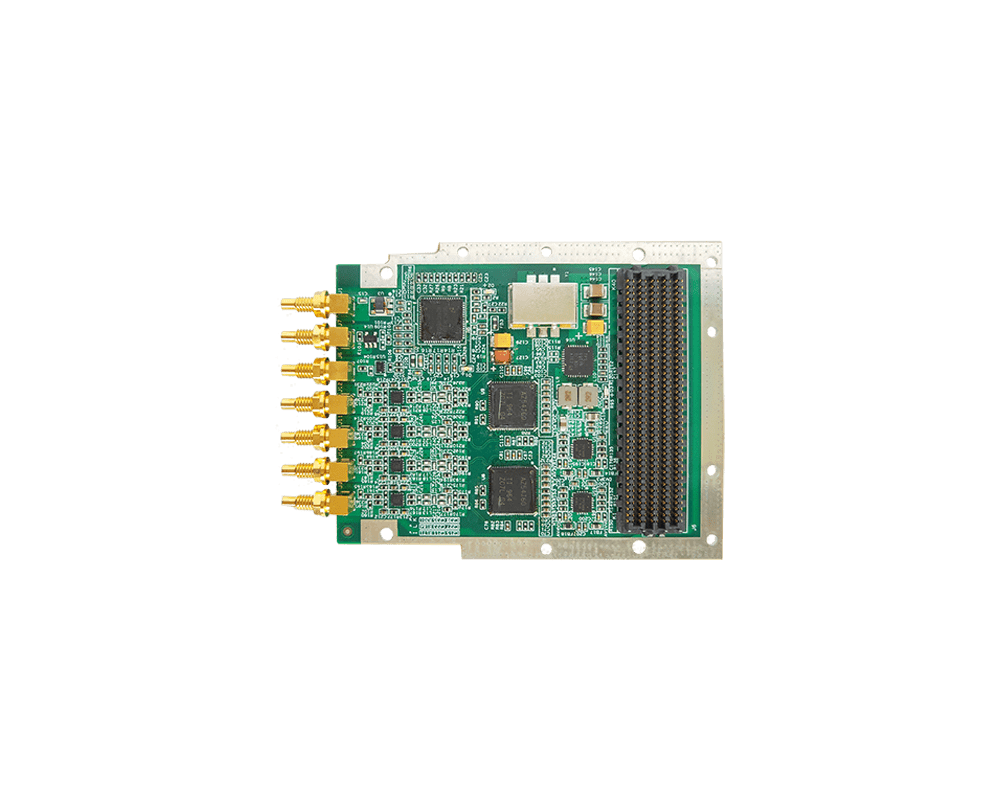

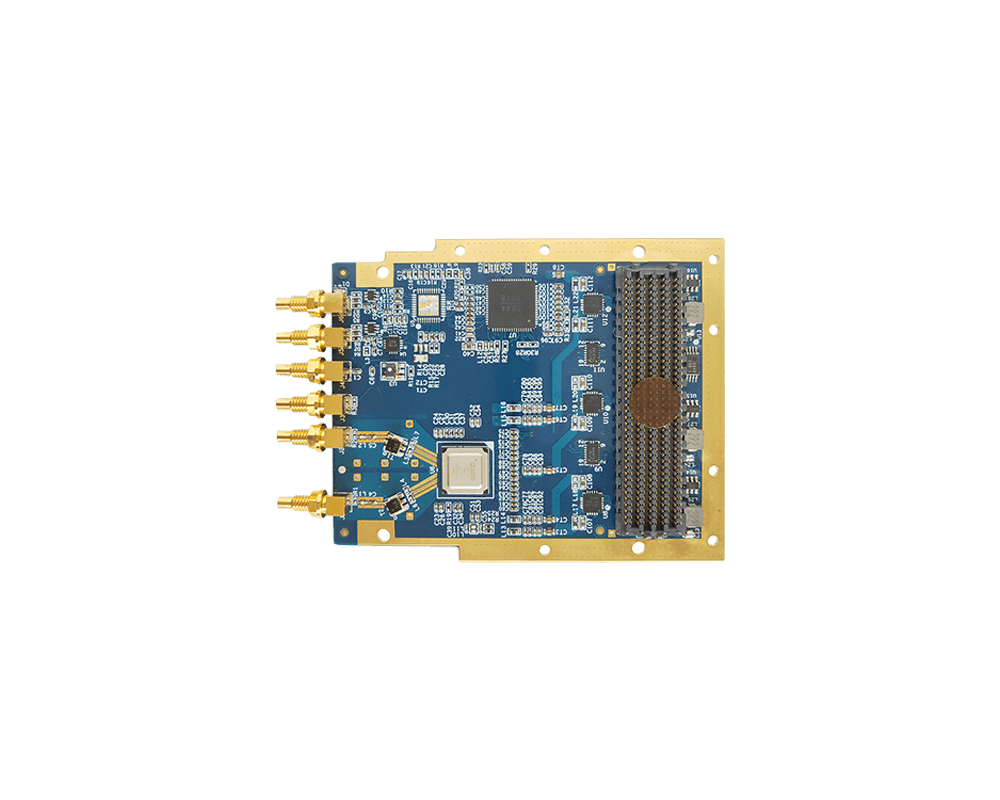

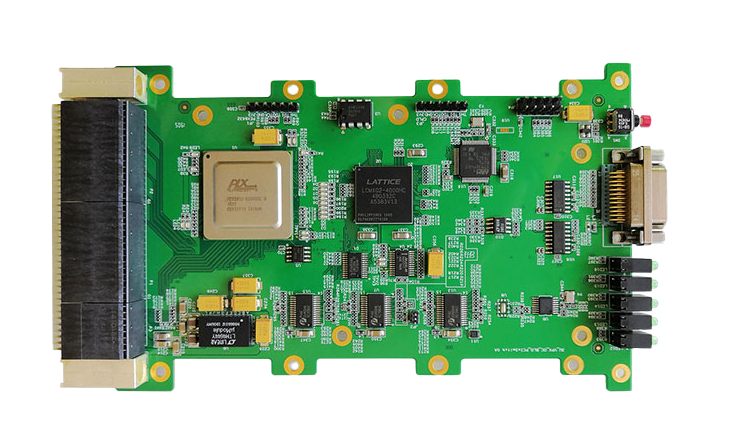

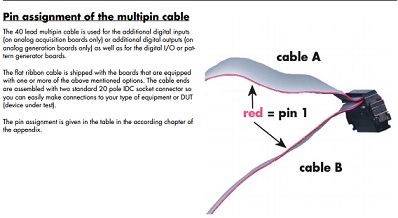

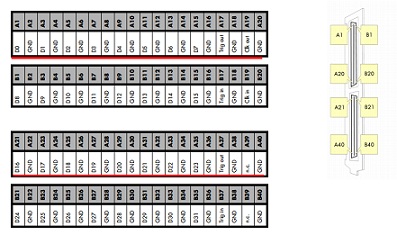

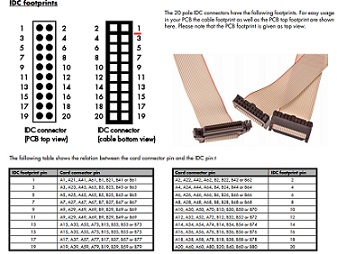

我們可以根據(jù)m2i.7011的datasheet中的管腳定義,,可以清晰的找到數(shù)字IO信號,、時鐘CLK信號、數(shù)字地信號GND等,。

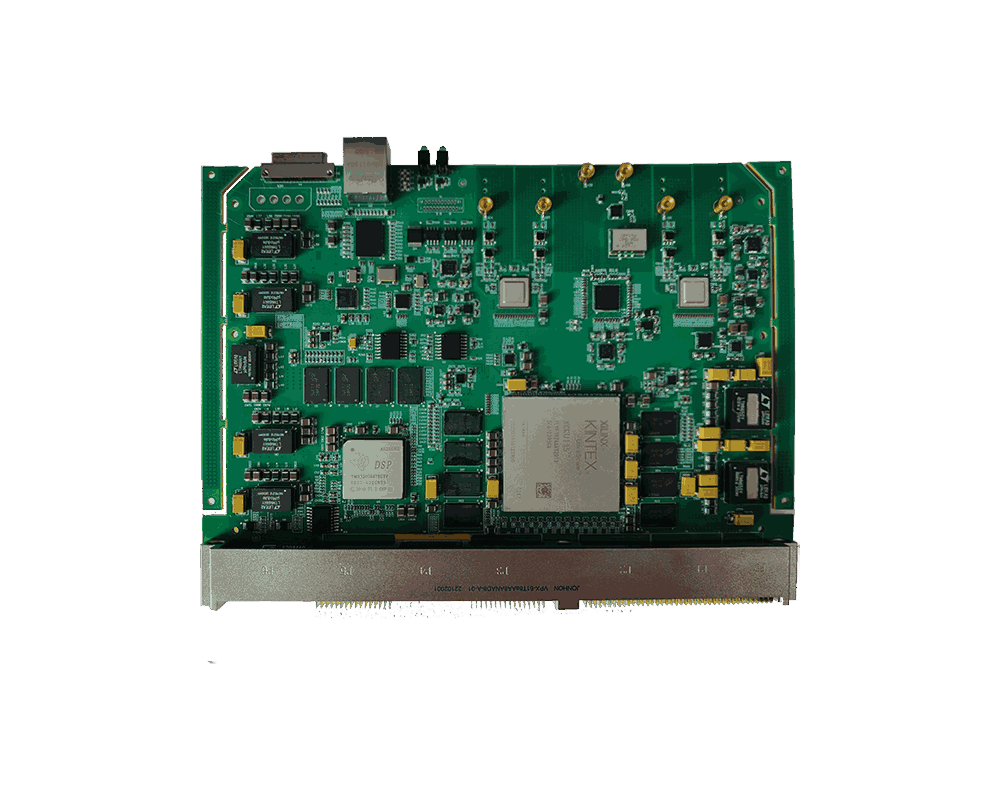

基于m2i.7011是大32bit的IO可以使用,,用戶需要20bit的數(shù)字IQ信號,其中包括I路信號10bit,,Q路信號10bit,還有1路clk輸入信號,,外加GND數(shù)字地信號,。

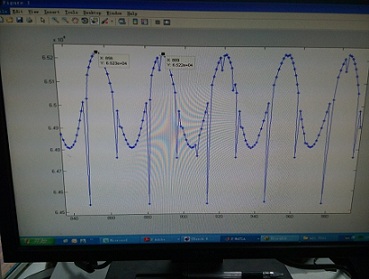

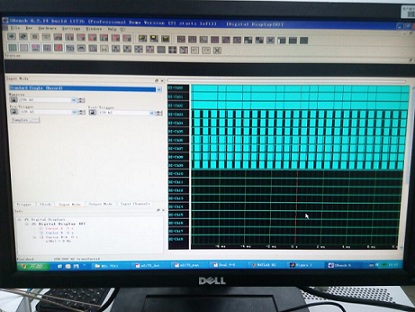

下圖是ADC采集的信號,用xilinx的chipscope軟件抓的ADC芯片量化出來的數(shù)據(jù),,可以看到采集的波形很平滑,。

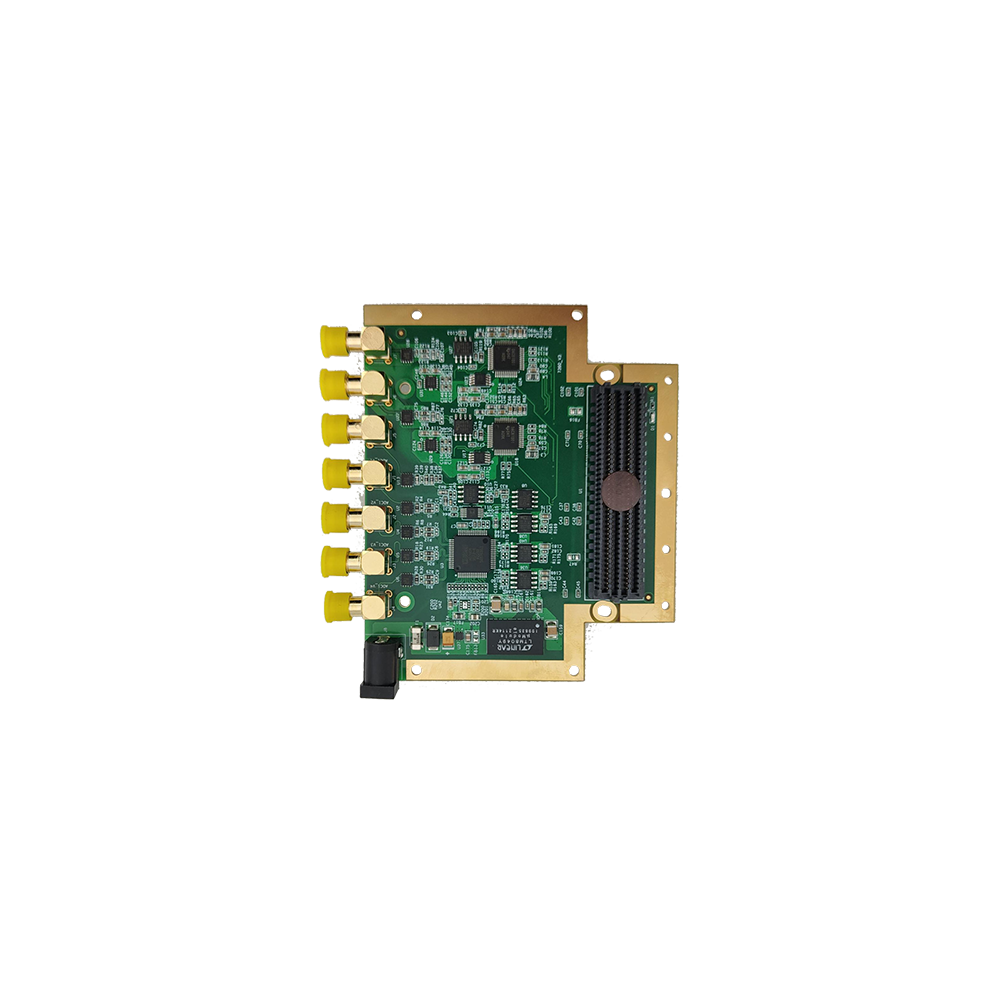

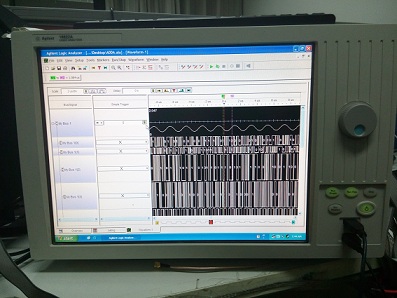

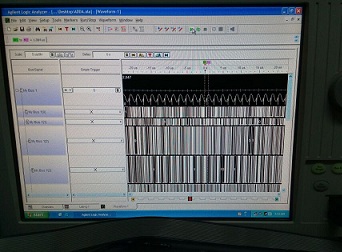

用Agilent 16822A Logic Analyzer測試ADC量化的10bit信號,如下圖所示,,因為邏輯分析儀有電平判決,,ADC 1.8V CMOS電壓也可以兼容,而且可以設(shè)置采樣的邊沿可以選擇rising edge還是falling edge,,再加上邏輯分析儀的電纜線可以做到屏蔽性好,、等長等特性。

下圖是用邏輯分析儀,,直接分析ADC量化的10bit的數(shù)據(jù),,不經(jīng)過FPGA處理。

2 io level

我們可以從m2i.7011數(shù)字IO卡的datasheet中,,可以知道,,IO卡對于高低電平的判決是高于2.0V當(dāng)成高電平1來處理,,低于0.8V當(dāng)成低電平0來處理。

The high level ≥2.0V

The low level ≤0.8V

m2i.7011對于高低電平的判決是datasheet寫的是3.3V,,5V的TTL電平標(biāo)準(zhǔn),。

即使我們把輸入阻抗impedance調(diào)節(jié)成110ohm,電壓是2.5V還是不兼容1.8V,。

但是采集藍牙信號的ADC芯片輸出的是1.8V的CMOS電平,,這樣電平不一致將導(dǎo)致IO卡無法預(yù)知高低電平的信號,一般高電平對于數(shù)字信號來說是1,,低電平是0,。如果無法正確的預(yù)判是1還是0,對于數(shù)字IO卡來說,,就會采集不到正確的0和1的值,。

所以,需要把ADC的數(shù)據(jù)先進入FPGA,,進行電平轉(zhuǎn)換,,轉(zhuǎn)換成3.3V的電平,為了和IO卡匹配,。轉(zhuǎn)換完之后,,需要把FPGA的的管腳引到IO口的插針上,但是引到IO插針上的時候,,用Agilent的邏輯分析儀,,采集原理和IO卡一樣,就是多了電平判決和采樣時鐘沿的選項,,這樣可以應(yīng)對許多種IO信號,。m2i.7011卡,電平不可以可選,,m4i.77xx是可以選擇電平標(biāo)準(zhǔn)的,,m2i.7011默認(rèn)是上升沿采集信號,不能使用下降沿采集信號,。

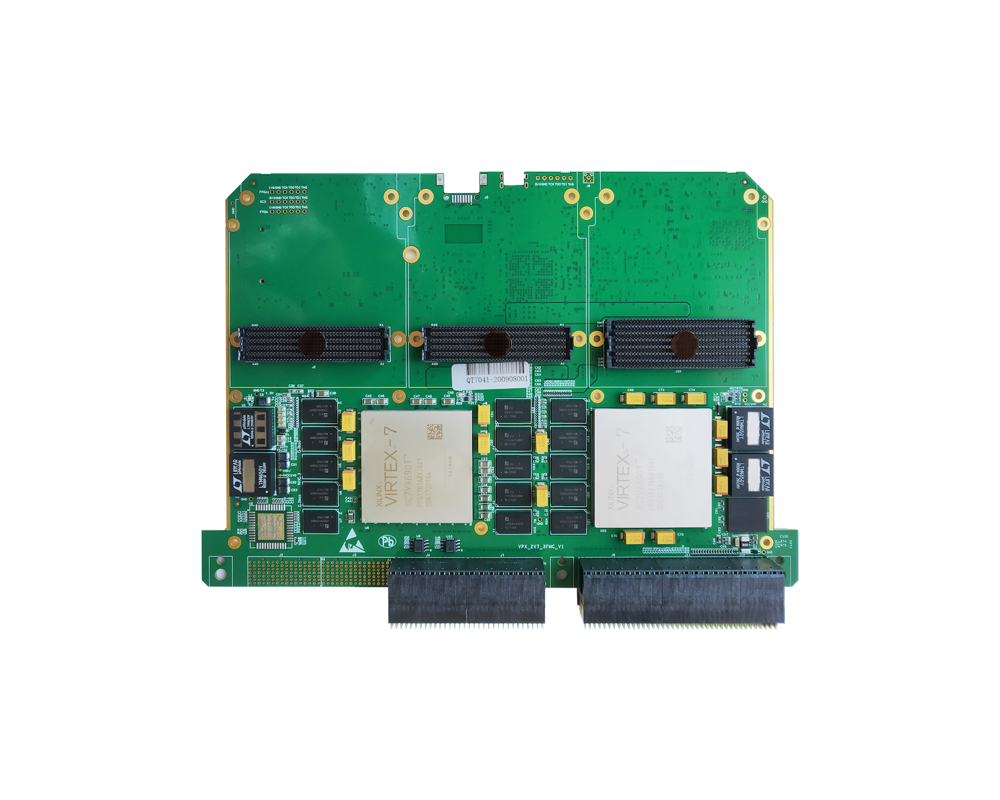

LEADCORE公司的ADC芯片設(shè)計比較怪異,,因為一般ADC芯片,TI或者ADI的ADC,,量化ADC數(shù)據(jù)adcdata的時候,,會有dclk,所謂dclk就是和adcdata一起同步出來的信號,,這樣時鐘和數(shù)據(jù)都是同步的,,但是LEADCORE公司的ADC芯片只有adcdata,沒有隨路時鐘dclk,,他們選擇的方式是FPGA這邊直接給1個16MHz的時鐘,,16MHz的時鐘使用xilinx公司的virtex-5信號DCM,,產(chǎn)生同頻率,相位分別為0°,,90°,,180°,270°的16MHz時鐘,,xilinx virtex-5芯片的DCM產(chǎn)生時鐘,,報低能產(chǎn)生32MHz的時鐘,但是產(chǎn)生16MHz的時鐘,,拿示波器量確實是16MHz,,可能是xilinx的一個bug。

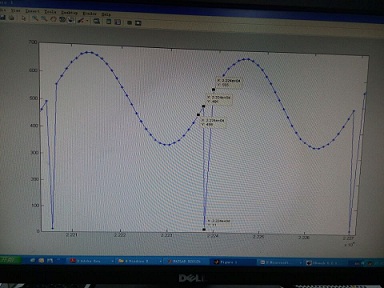

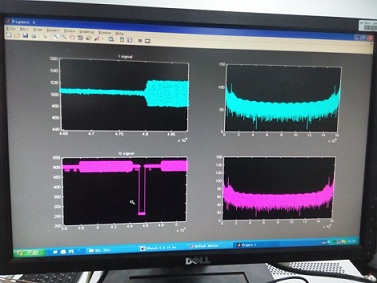

DCM產(chǎn)生的4個時鐘里面,,有1個或者2個,,可以讓dclk和adcdata盡量的滿足setup time和hold time,保證采集的數(shù)據(jù)在時序上沒有violation,。這樣就能避免出現(xiàn)下圖的現(xiàn)象:

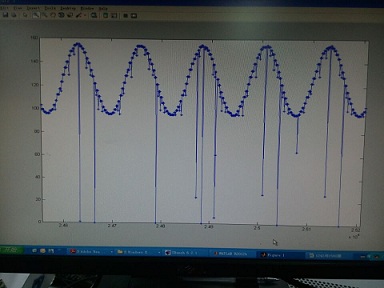

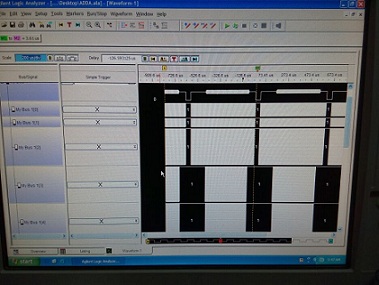

實際測試,,發(fā)現(xiàn)沒有了IO delay的錯誤,反而多了一個周期性的干擾的毛刺,,而且毛刺的位置非常固定,。拿Agilent Logic Analyzer測試10bit的IO數(shù)據(jù),發(fā)現(xiàn)在1個周期的sinus波形里有個周期性的干擾,。

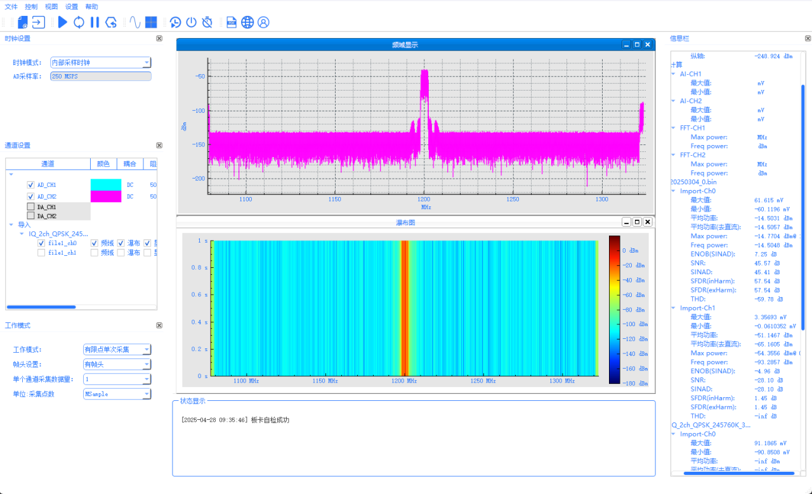

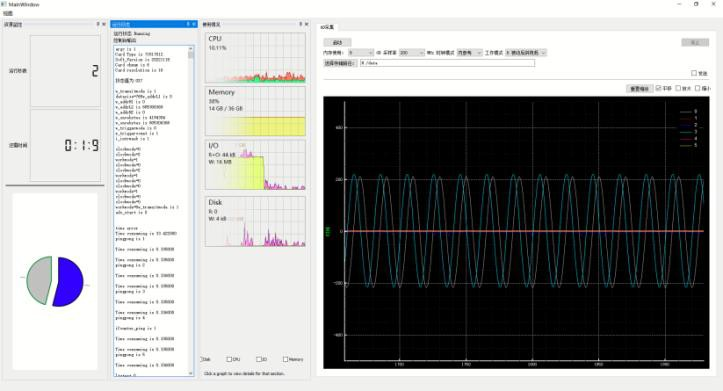

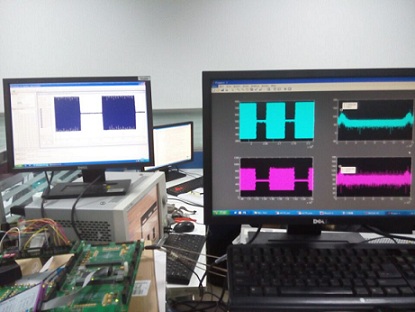

后再拿m2i.7011數(shù)字IO卡,,測試,采集完存成bin文件,,用MATLAB觀察,,現(xiàn)象和Agilent的邏輯分析儀現(xiàn)象一致。

再仔細(xì)觀察突變的位置,,剛好是512左右,我們再分析10bit的數(shù)據(jù)1000000000是512,,也就是說剛好高位從0到1翻轉(zhuǎn)的過程中突變了,,導(dǎo)致1變成0,導(dǎo)致數(shù)據(jù)突然下跌,。

我們知道,,對于數(shù)字電路來說,10bit的數(shù)據(jù),,在邏輯里面如果經(jīng)過D觸發(fā)器,,10bit的數(shù)據(jù)要發(fā)生翻轉(zhuǎn)都在在時鐘的上升沿或時鐘的下降沿,因為D觸發(fā)器屬于邊沿觸發(fā)器,。對于邊沿比較敏感,。

那10bit的數(shù)據(jù),,就需要10個D觸發(fā)器,每個觸發(fā)器存1bit的值,,那如果是由時鐘邊沿引起的第10bit的數(shù)據(jù),,周期性的翻轉(zhuǎn)受干擾,那我們就用上面DCM產(chǎn)生的4個相位的時鐘,,分別試驗,。

如果4個時鐘都是同樣的現(xiàn)象,就可以定位是硬件上的問題了,。

終,,經(jīng)過試驗,發(fā)現(xiàn)是ADC芯片引出的IO上有問題,,所以更換了IO,,重新采集??梢圆杉狡交膕inus波形,。

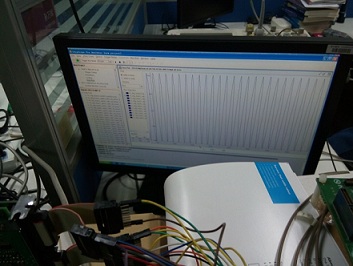

3 bluetooth signal

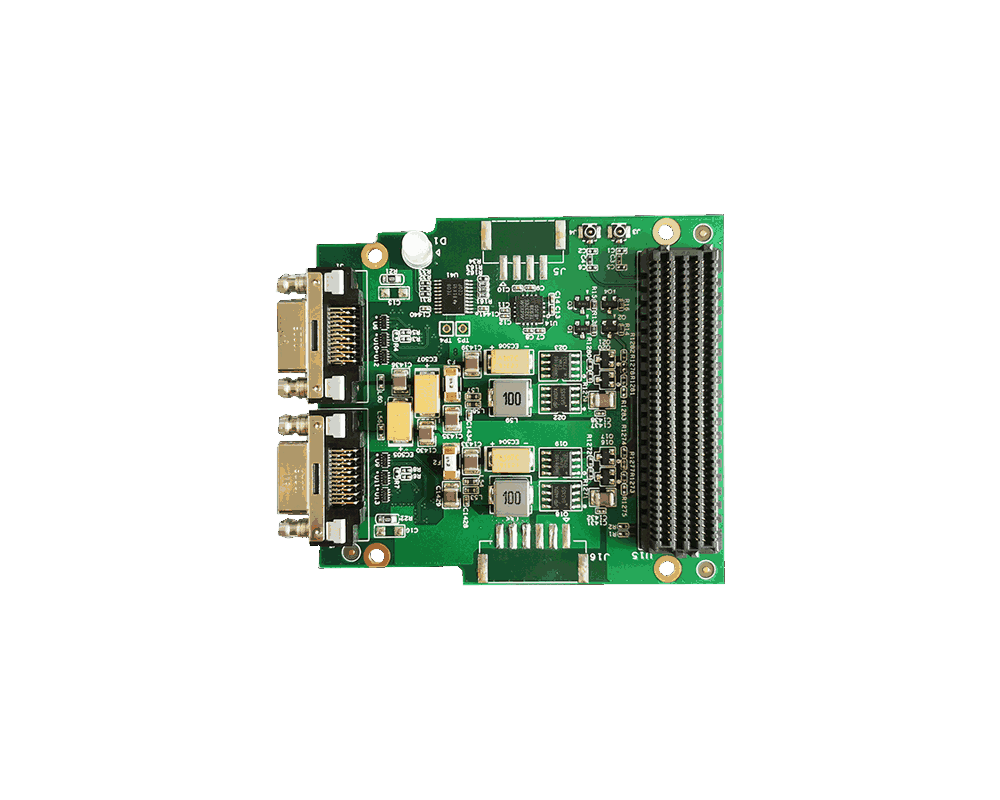

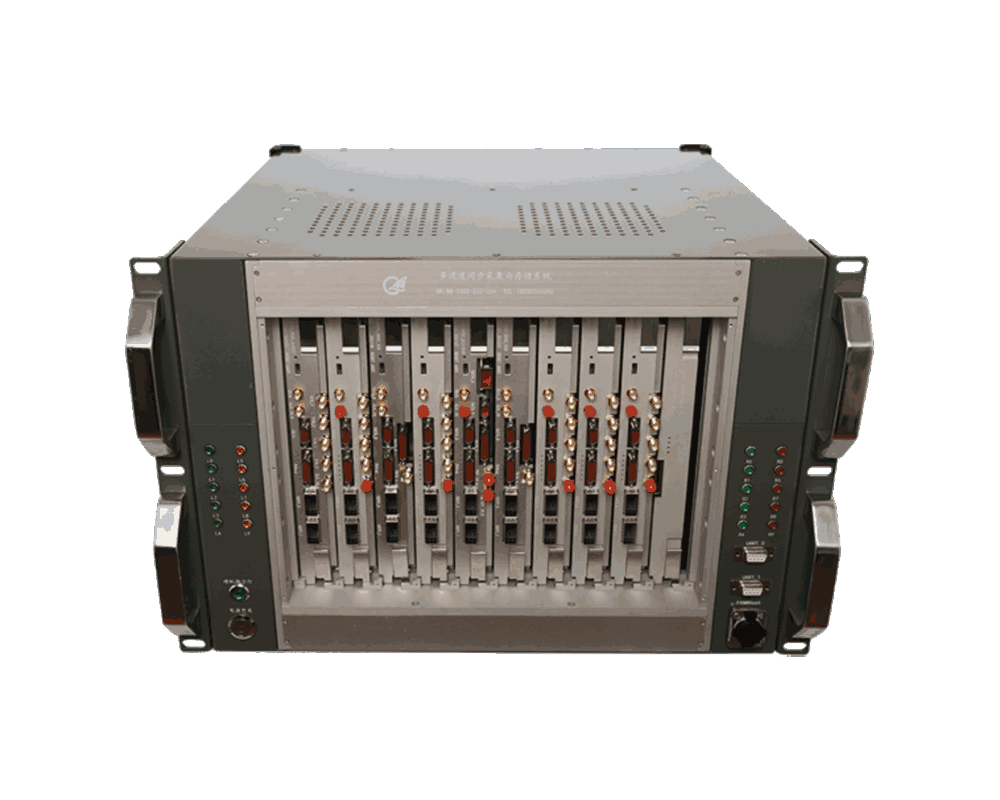

使用Agilent基于移動領(lǐng)域的WiMAX矢量信號源MXG,,產(chǎn)生藍牙信號包,,藍牙包里可以疊加噪聲。

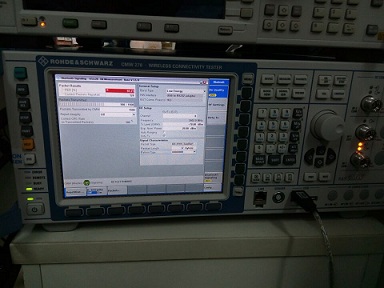

使用Rohde&Schwarz公司的無線通信CMW270,,可以統(tǒng)計藍牙包的誤報率,。

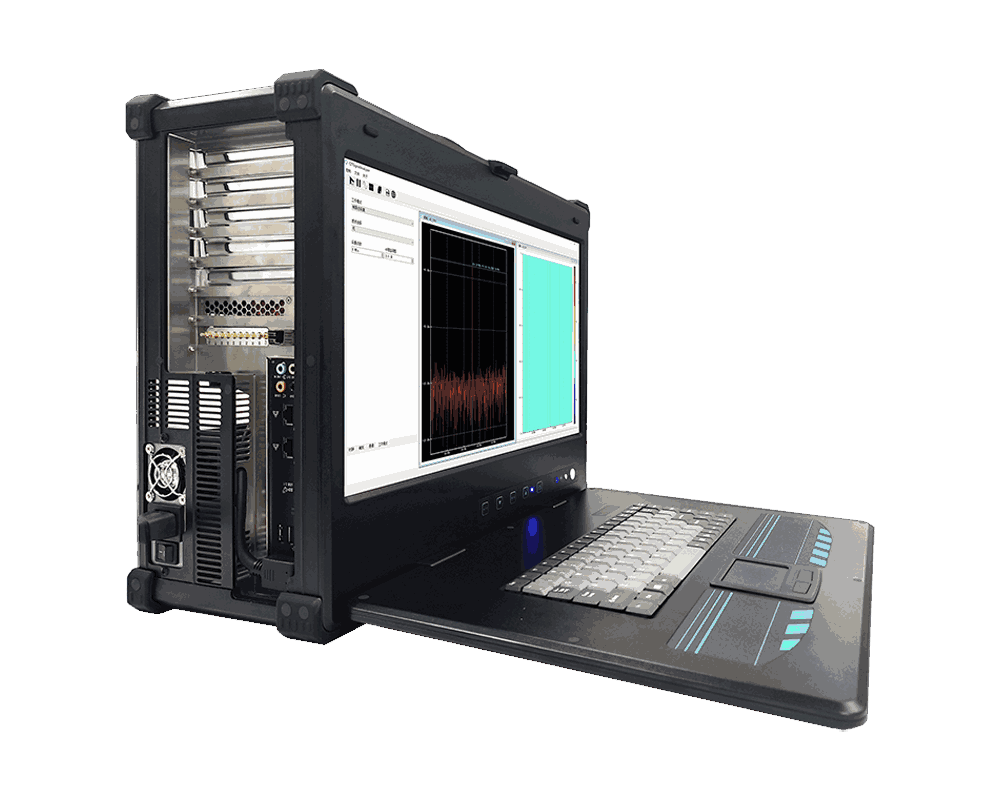

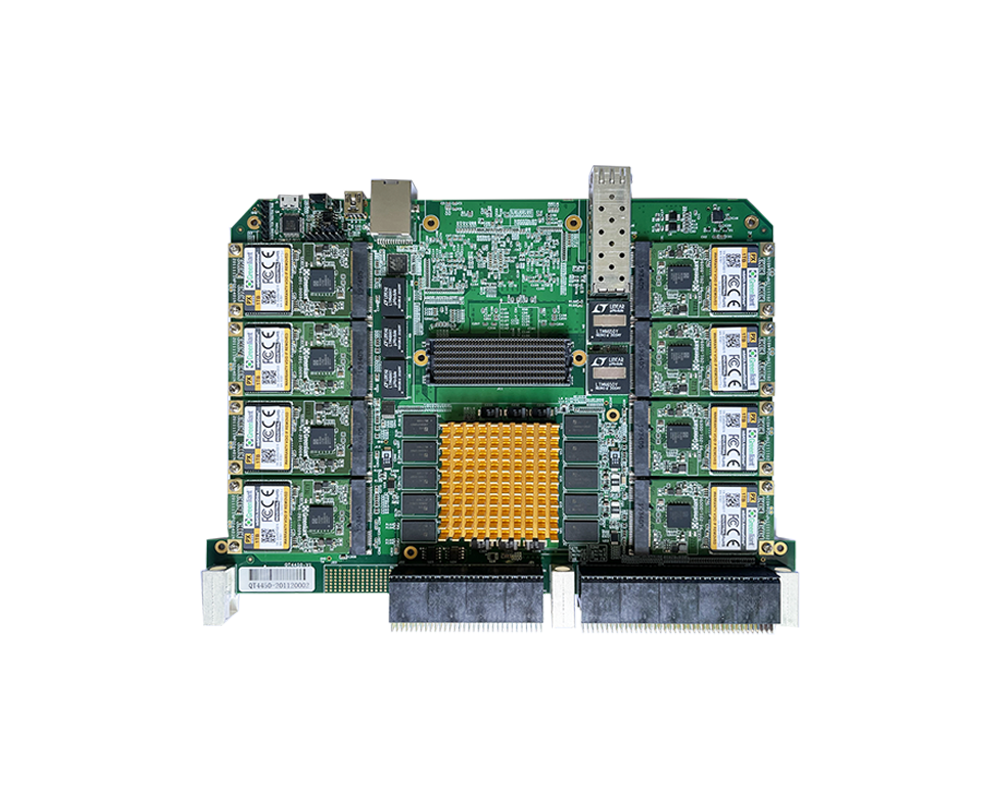

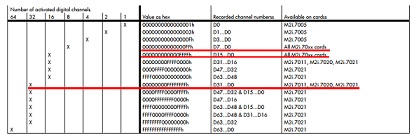

當(dāng)把一切環(huán)境都搭建好,可以使用m2i.7011采集數(shù)字IO信號了,,數(shù)字IO卡使能的bit數(shù)可以從datasheet知道,。

8bit、16bit,、32bit,,因為采集IQ兩路總共需要20bit,還需要1bit GND和1bit CLK,,所以需要使能32bit的IO,,采樣時鐘選擇外時鐘16MHz。

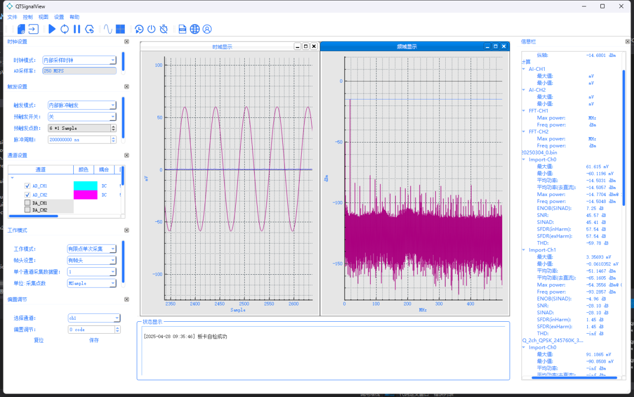

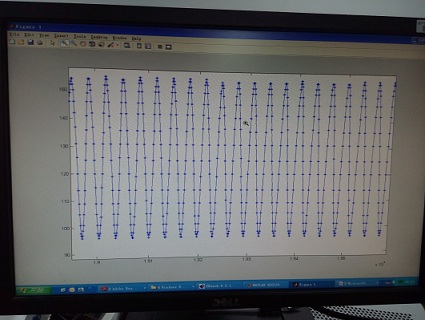

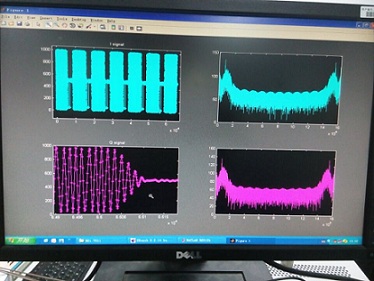

下圖是使用m2i.7011采集的IQ藍牙包IO波形,。

同樣用Agilent的邏輯分析儀看到藍牙包是一包一包出現(xiàn)的,。

我們使用chipscope抓取藍牙包,使用MATLAB把采集的32bit的IO數(shù)據(jù)進行解析,,會看到IQ兩路的藍牙包,。

藍牙包根據(jù)不同的疊加噪聲會有不同的時域表現(xiàn)。

4 summary

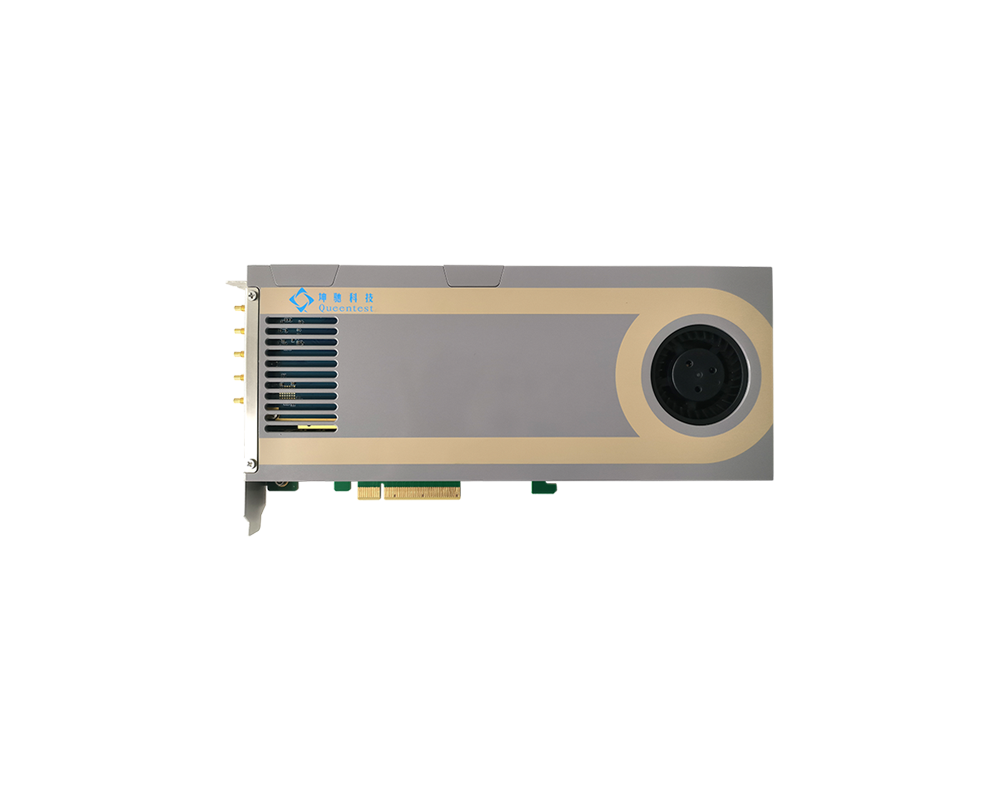

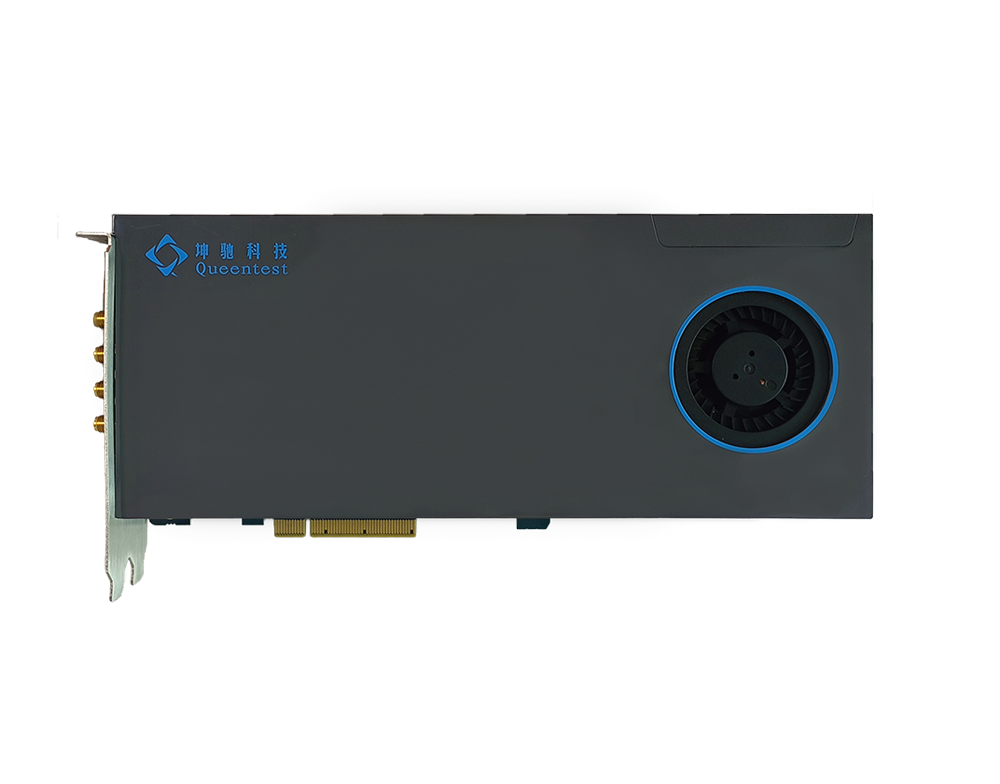

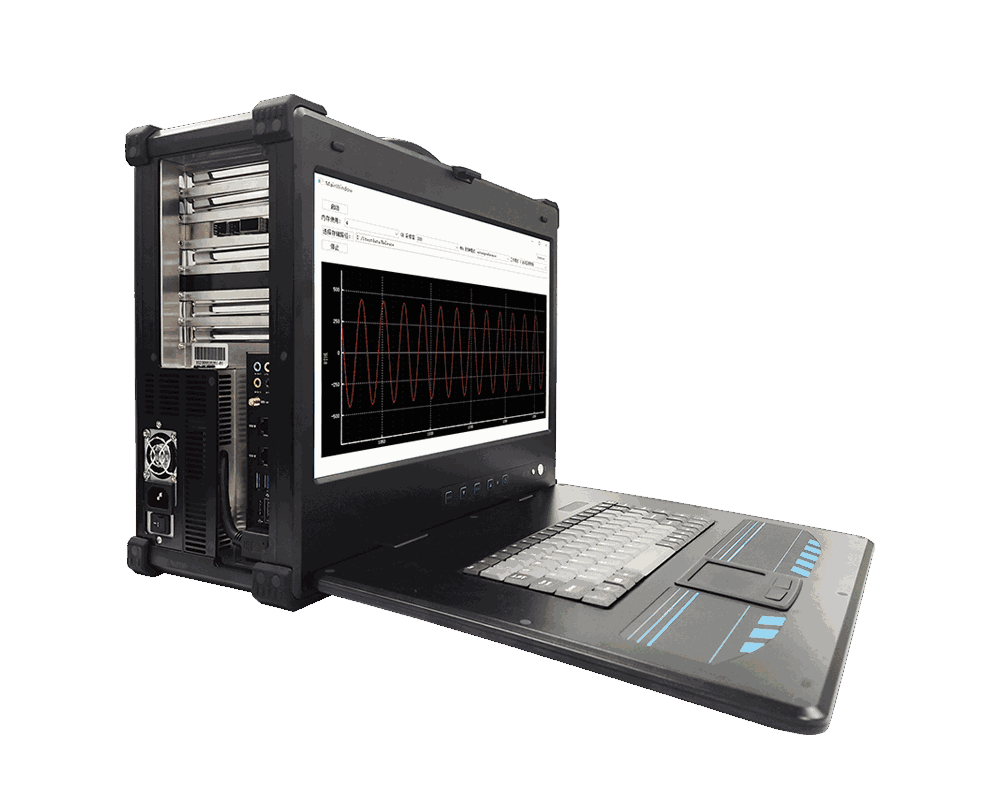

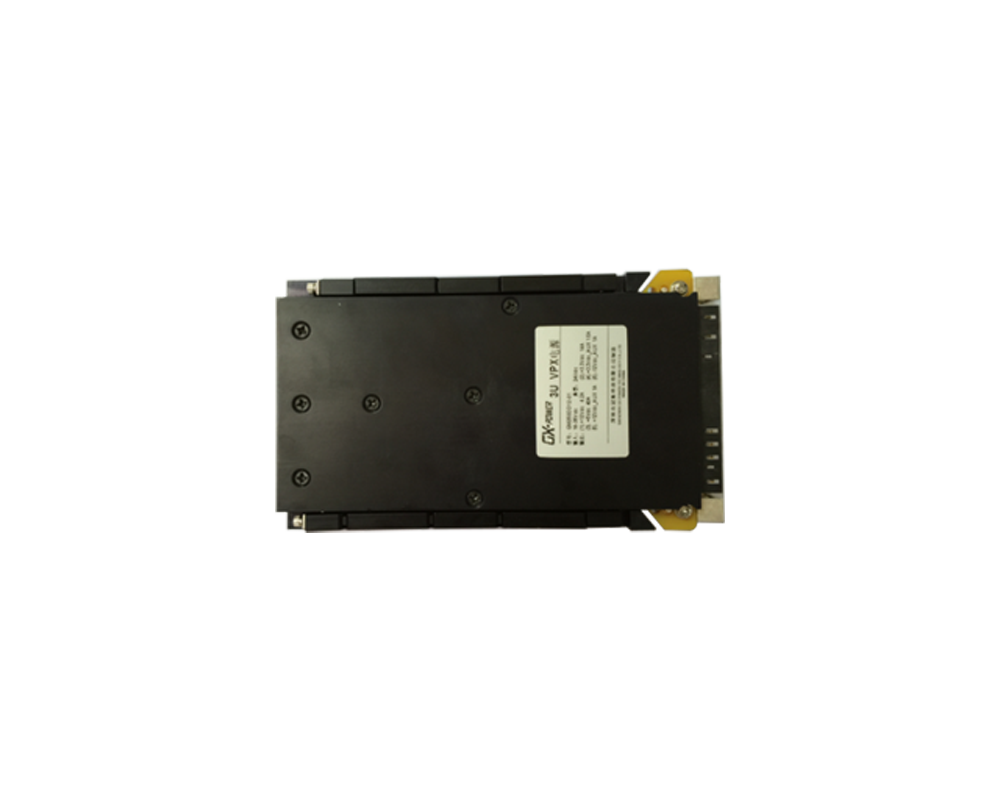

北京坤馳科技的數(shù)字IO卡基于采集的是數(shù)字IO信號,每個IO口對應(yīng)1bit的數(shù)據(jù),,其功能類似于邏輯分析儀,,IO卡的優(yōu)點在于體積小,可攜帶,,可插與普通電腦或者便攜式機的PCIE或PCI插槽使用,,接口形式示采集卡是PCI還是PCIE接口。數(shù)字IO卡支持可編程,,支持多個IO,,多可使用64個IO口,相比于Agilent 16822A邏輯分析儀,,邏輯分析儀缺點是數(shù)字IO口少,,只支持16個數(shù)字IO口和1個CLK和1個GND,無法滿足2路IQ產(chǎn)生的20bit數(shù)字信號,。